## Efficient FPGA Implementation and Power Modelling of Image and Signal Processing IP Cores

A thesis submitted for the degree of Doctor of Philosophy

by

Shrutisagar Chandrasekaran B.E.

Electronic and Computer Engineering School of Engineering and Design Brunel University, West London May 2007

| Additional comments: _ | <br> | <br> |  |

|------------------------|------|------|--|

|                        |      |      |  |

|                        |      |      |  |

Part B, when complete, should be returned to the Assistant Registrar (Graduate Studies).

For the attention of candidates who have completed Part A

- i) Attention is drawn to the fact that the copyright of a thesis rests with its author.

- ii) A copy of a candidate's thesis is supplied to the University Library on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author or University, as appropriate.

Requests for such permission should be addressed in the first instance to the Head of Library Services.

#### Abstract

Field Programmable Gate Arrays (FPGAs) are the technology of choice in a number of image and signal processing application areas such as consumer electronics, instrumentation, medical data processing and avionics due to their reasonable energy consumption, high performance, security, low design-turnaround time and reconfigurability. Low power FPGA devices are also emerging as competitive solutions for mobile and thermally constrained platforms. Most computationally intensive image and signal processing algorithms also consume a lot of power leading to a number of issues including reduced mobility, reliability concerns and increased design cost among others. Power dissipation has become one of the most important challenges, particularly for FPGAs. Addressing this problem requires optimisation and awareness at all levels in the design flow. The key achievements of the work presented in this thesis are summarised here.

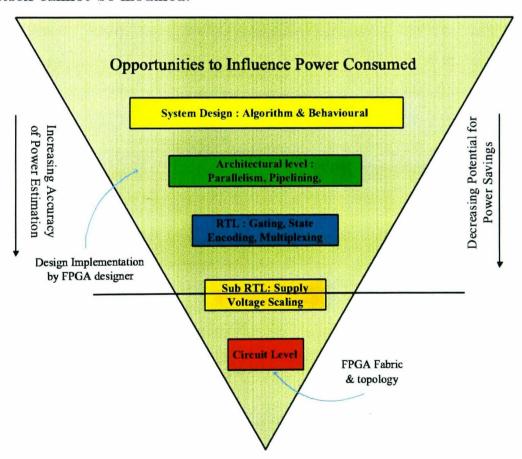

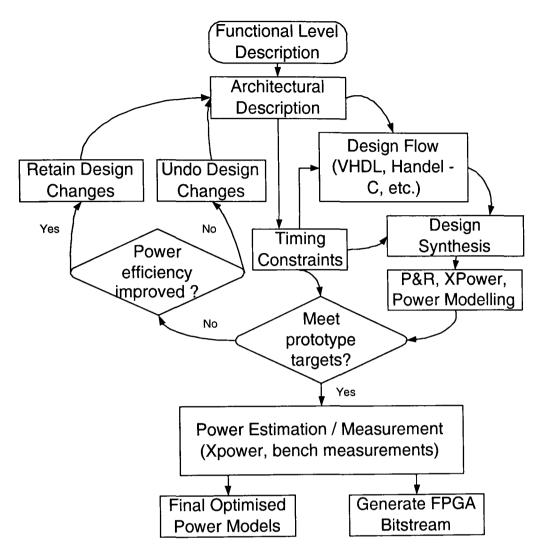

Behavioural level optimisation strategies have been used for implementing matrix product and inner product through the use of mathematical techniques such as Distributed Arithmetic (DA) and its variations including offset binary coding, sparse factorisation and novel vector level transformations. Applications to test the impact of these algorithmic and arithmetic transformations include the fast Hadamard/Walsh transforms and Gaussian mixture models. Complete design space exploration has been performed on these cores, and where appropriate, they have been shown to clearly outperform comparable existing implementations. At the architectural level, strategies such as parallelism, pipelining and systolisation have been successfully applied for the design and optimisation of a number of cores including colour space conversion, finite Radon transform, finite ridgelet transform and circular convolution. A pioneering study into the influence of supply voltage scaling for FPGA based designs, used in conjunction with performance enhancing strategies such as parallelism and pipelining has been performed. Initial results are very promising and indicated significant potential for future research in this area.

A key contribution of this work includes the development of a novel high level power macromodelling technique for design space exploration and characterisation of custom IP cores

for FPGAs, called Functional Level Power Analysis and Modelling (FLPAM). FLPAM

is scalable, platform independent and compares favourably with existing approaches. A

hybrid, top-down design flow paradigm integrating FLPAM with commercially available

design tools for systematic optimisation of IP cores has also been developed.

# Certificate of Originality

I hereby certify that the work presented in this thesis is my original research and has not been presented for a higher degree at any other university or institute.

(Shrutisagar Chandrasekaran)

To my parents

### Acknowledgements

While one does not happen to notice time fly by during the course of a PhD program, the actual process of writing the dissertation can be an eye opening experience. As I put the finishing touches to my thesis, the personal and practical support of numerous people who have helped me through this process immediately springs to my mind.

First and foremost, I would like to thank my parents for being there (a phone call away, considering the distances involved) whenever the need arose. Special mention goes to my mother for her uncanny knack of tuning into my feelings and for her incredible ability to roll up love, patience, encouragement and realism into one package. Thank you dad for being my constant sounding board in all practical matters, small or great and for teaching me the value of objectivity in every action.

This PhD would not have been possible at all, without the constant support, encouragement, motivation and most importantly constructive criticism provided by my supervisor, Dr. Abbes Amira. Cliched as the previous statement sounds, it is true in every sense. Although an extremely tough taskmaster, I greatly value the opportunity of working with him.

I would like to acknowledge the collaborative support provided by Prof. Amine Bermak of HKUST and Prof. P. K. Meher of NTU. Along the way, a number of colleagues, friends and acquaintances have enriched my life at Belfast, Hong Kong and London. Due to the impracticality of naming everyone and to avoid missing out someone inadvertently, I would like to just say - thank you all for the times we have spent together. Special mention would go to Ravi Kiran for listening to my rants patiently at all times of the day and night.

#### Author's Publication

#### Journal Papers

- 1. A. Amira and S. Chandrasekaran, "Power Modeling and Efficient FPGA Implementation of FHT for Signal Processing", *IEEE Transactions on VLSI Systems*, vol. 15, no. 3, pp. 286-295, March 2007

- 2. S. Chandrasekaran and A. Amira, "Power Modelling and Acceleration of Finite Radon Transform on Reconfigurable Hardware", *IEEE Transactions on Computers*, In Revision

- 3. A. Amira, S. Chandrasekaran, D. W. G. Montgomery and I S Uzun, "High Performance Implementation of PET Segmentation using a Multiresolution-Statistical Approach", Elsevier Neurocomputing Special Issue on Vision Research, Submitted

- 4. P. K. Meher, S. Chandrasekaran and A. Amira, "FPGA Realization of FIR Filters by Efficient and Flexible Systolization Using Distributed Arithmetic", *IEEE Transactions on Signal Processing*, Submitted

#### Conference Papers (selected)

S. Chandrasekaran, A. Amira, A. Bermak and M. Shi, "Performance Enhanced Voltage Scaling in FPGAs", *International Symposium on Integrated Circuits* (ISIC) 2007, September 26<sup>th</sup> - 28<sup>th</sup>, Singapore

- 2. M. Shi, S. Chandrasekaran, A. Bermak and A. Amira, "FPGA Based Run Time Reconfigurable Gas Discrimination System", *International Symposium on Integrated Circuits (ISIC) 2007*, September 26<sup>th</sup> 28<sup>th</sup>, Singapore

- S. Chandrasekaran and A. Amira, "A General Framework for Efficient FPGA Implementation and Power Modelling of Image Processing Cores", IET Visual Information Engineering 2007 Conference, July 25<sup>th</sup> – 27<sup>th</sup>, London, UK

- A. Amira, S. Chandrasekaran and D. Skinner, "A Fast Hybrid LSI Approach for Intelligent Information Retrieval", *IET Visual Information Engineering* 2007 Conference, July 25<sup>th</sup> – 27<sup>th</sup>, London, UK

- 5. S. Chandrasekaran and A. Amira, "A New Behavioural Power Modelling Approach for FPGA based Custom Cores", 2007 NASA/ESA Conference on Adaptive Hardware and Systems, August  $5^{th} 8^{th}$ , Edinburgh, Scotland, UK

- 6. S. Chandrasekaran and A. Amira, "Novel Sparse OBC Based Distributed Arithmetic Architecture for Matrix Transforms", 2007 IEEE International Symposium on Circuits and Systems, May 27<sup>th</sup> – 30<sup>th</sup>, New Orleans, USA

- 7. F. Bensaali, S. Chandrasekaran, A. Amira, "Power Modeling and Efficient FPGA Implementation of Color Space Conversion", 13<sup>th</sup> IEEE International Conference on Electronics, Circuits and Systems 2006, December 10<sup>th</sup> – 13<sup>th</sup>, Nice, France

- M. Shi, A. Bermak, S. Chandrasekaran, A. Amira, "An Efficient FPGA Implementation of Gaussian Mixture Models-Based Classifier Using Distributed Arithmetic", 13<sup>th</sup> IEEE International Conference on Electronics, Circuits and Systems 2006, December 10<sup>th</sup> 13<sup>th</sup>, Nice, France

- S. Chandrasekaran and A. Amira, "Multi-Level Parallelism for Power and Energy Aware Design Verified Using Novel Functional Level Power Analysis & Modelling (FLPAM)", NASA Military and Aerospace Applications of Programmable Devices and Technologies Conference 2006, September 26<sup>th</sup> 28<sup>th</sup>, Washington DC, USA

- 10. S. Chandrasekaran and A. Amira, "FPGA Implementation and Power Modeling of FWT for Pattern Recognition", NASA Military and Aerospace Applications of Programmable Devices and Technologies Conference 2006, September 26<sup>th</sup> 28<sup>th</sup>, Washington DC, USA

- 11. S. Chandrasekaran and A. Amira, "FPGA Implementation And Power Modelling of the Fast Walsh Transform", International Conference on Field Programmable Logic and Applications (FPL), August 28<sup>th</sup> 30<sup>th</sup> 2006, Madrid, Spain

- 12. S. Chandrasekaran and A. Amira, "Power Reduction For FPGA Implementations: Design Optimisation And High Level Modelling", International Conference on Field Programmable Logic and Applications (FPL), August 28<sup>th</sup> 30<sup>th</sup> 2006, Madrid, Spain

- 13. S. Chandrasekaran and A. Amira, "High Speed Energy Efficient Architectures for Finite Ridgelet Transform", NASA Military and Aerospace Applications of Programmable Devices and Technologies Conference 2005, September 7<sup>th</sup> 9<sup>th</sup>, Washington DC, USA

- 14. S. Chandrasekaran, A. Amira and F. Bensaali, "FPGA Implementation of Reduced Bit Plane Motion Estimation", NASA Military and Aerospace Applications of Programmable Devices and Technologies Conference 2005, September 7<sup>th</sup> 9<sup>th</sup>, Washington DC, USA

- 15. S. Chandrasekaran and A. Amira, "High Speed / Low Power Architectures for the Finite Radon Transform", International Conference on Field Programmable Logic and Applications (FPL), August 24<sup>th</sup> 26<sup>th</sup> 2005, Tampere, Finland

- 16. S. Chandrasekaran and A. Amira, "An Area Efficient Low Power Inner Product Computation for Discrete Orthogonal Transforms", IEEE International Conference on Image Processing (ICIP), September 11<sup>th</sup> 14<sup>th</sup> 2005, Genoa, Italy

- 17. S. Chandrasekaran and A. Amira, "A Novel Methodology for Temporal Partitioning in Self Reconfigurable Driven Multicontext FPGA", Postgraduate Research Conference in Electronics, Photonics, Communications and Networks, and Computing Science (PREP) 2005, March 30<sup>th</sup>— April 1<sup>st</sup> 2005, Lancaster, UK

- 18. S. Chandrasekaran and A. Amira, "An FPGA based Accelerator for the Finite Ridgelet Transform", IEEE International Computer Systems and Information Technology Conference 05, July 19<sup>th</sup> – 21<sup>st</sup> 2005, Algiers, Algeria

- 19. S. Chandrasekaran and N. S. Krishnan, "Double Abstraction Level Heuristic Power Optimization for Digital Signal Processors", 46<sup>th</sup> IEEE International Midwest Symposium on Circuits & Systems, December 27<sup>th</sup> – 30<sup>th</sup> 2003, Cairo, Egypt

- 20. S. Chandrasekaran and H. Pattabhiraman, "Automatic Damage Detection for Railroad Tracks by Real Time DSP Based Dual Analysis System", 46<sup>th</sup> IEEE International Midwest Symposium on Circuits and Systems, December 27<sup>th</sup> – 30<sup>th</sup> 2003, Cairo, Egypt

# Contents

|                      | Abs  | stract   |                                                                | iii  |

|----------------------|------|----------|----------------------------------------------------------------|------|

|                      | Dec  | laratio  | on                                                             | iv   |

|                      | Ack  | dgements | vi                                                             |      |

| Author's Publication |      |          |                                                                |      |

|                      | List | of Ab    | breviations                                                    | xxvi |

| 1                    | Intr | oducti   | ion                                                            | 1    |

|                      | 1.1  | Hardw    | vare Acceleration                                              | . 2  |

|                      |      | 1.1.1    | Digital Signal Processors                                      | . 3  |

|                      |      | 1.1.2    | Special Purpose Application Specific Integrated Circuits Hard- |      |

|                      |      |          | ware                                                           | . 4  |

|                      | 1.2  | Field    | Programmable Gate Arrays: A Review                             | . 5  |

|                      |      | 1.2.1    | FPGA Structure                                                 | . 6  |

|                      |      | 1.2.2    | FPGA Design Entry and Synthesis                                | . 7  |

|                      | 1.3  | Oppor    | tunities in Deploying FPGA Based Solutions                     | . 8  |

|                      |      | 1.3.1    | The Importance of FPGAs in Digital Logic Implementation        | . 8  |

|                      |      | 1.3.2    | In Field Design Upgradation and Future Proofing                | . 9  |

|                      | 1.4  | Design   | Challenges in Deploying FPGA Based Solutions                   | . 10 |

|                      |      | 1.4.1    | The Need for Core Based Design                                 | . 10 |

|                      |      | 1.4.2    | The Importance of Power Aware Design                           | . 11 |

|                      | 1.5  | Resear   | rch Objectives and Motivations                                 | . 16 |

|                      | 1.6  | Overa    | ll Project Strategy                                            | . 16 |

| Contents | xii |

|----------|-----|

|          |     |

|   | 1.7    | IP Cor  | e Selection Strategy                                           | 19 |

|---|--------|---------|----------------------------------------------------------------|----|

|   | 1.8    | Organi  | sation of the Thesis                                           | 20 |

| ก | T :4.5 |         | Davious                                                        | 00 |

| 2 |        |         | Review                                                         | 22 |

|   | 2.1    |         | action                                                         | 22 |

|   | 2.2    |         | Implementations of Selected Matrix Algorithms and Related      |    |

|   |        | Archite | ectures                                                        | 23 |

|   |        | 2.2.1   | Existing Architectures and FPGA Implementations of the Walsh   |    |

|   |        |         | / Hadamard Transform                                           | 23 |

|   |        | 2.2.2   | Architectures for Higher Dimensional Algorithms for Multires-  |    |

|   |        |         | olution Methods: The Finite Radon & Ridgelet Transforms .      | 29 |

|   |        | 2.2.3   | Architectures for Colour Space Conversion                      | 34 |

|   |        | 2.2.4   | Application Specific Hardware Implementation of Gaussian       |    |

|   |        |         | Mixture Modelling                                              | 39 |

|   |        | 2.2.5   | FPGA Implementation of Finite Digital Convolution              | 40 |

|   | 2.3    | Power   | Modelling                                                      | 43 |

|   |        | 2.3.1   | Versatile Place and Route Based FPGA Power Models              | 43 |

|   |        | 2.3.2   | Probabilistic Power Prediction for the Xilinx 4000-Series FPGA | 44 |

|   |        | 2.3.3   | Cycle Accurate Energy Measurement and Characterisation of      |    |

|   |        |         | FPGAs                                                          | 45 |

|   |        | 2.3.4   | High-Level Power Modelling of CPLDs and FPGAs                  | 45 |

|   |        | 2.3.5   | Macromodels for High Level Area and Power Estimation on        |    |

|   |        |         | FPGAs                                                          | 46 |

|   |        | 2.3.6   | Methodology for High Level Estimation of FPGA Power Con-       |    |

|   |        |         | sumption                                                       | 48 |

|   |        | 2.3.7   | Post Synthesis Level Power Modelling of FPGAs                  | 49 |

|   |        | 2.3.8   | Power Estimation and Power Measurement of Xilinx Virtex        |    |

|   |        |         | FPGAs: Trade-offs and Limitations                              | 50 |

|   |        | 2.3.9   | Power Estimation for Cycle-Accurate Functional Descriptions    |    |

|   |        |         | of Hardware                                                    | 51 |

|   |        | 2.3.10  | Dynamic Power Estimation Technique for FPGAs                   | 52 |

|   |        |         | -                                                              |    |

|   |      | 2.3.11  | Power Modelling and Characteristics of Field Programmable    |     |

|---|------|---------|--------------------------------------------------------------|-----|

|   |      |         | Gate Arrays                                                  | 53  |

|   |      | 2.3.12  | Brief Review of selected ASIC Power Modelling Techniques     | 54  |

|   | 2.4  | Archit  | ectural Optimisations for Performance Power Tradeoffs        | 56  |

|   | 2.5  | Shorte  | comings and Disadvantages of Existing Work                   | 59  |

|   | 2.6  | Conclu  | isions                                                       | 61  |

| 3 | IP ( | Core O  | ptimisations at Algorithmic and Behavioural Level            | 63  |

|   | 3.1  | Introd  | uction                                                       | 63  |

|   | 3.2  | An Ar   | rea Efficient Low Power Inner Product Computation For Dis-   |     |

|   |      | crete ( | Orthogonal Transforms                                        | 64  |

|   |      | 3.2.1   | Mathematical Basis                                           | 65  |

|   |      | 3.2.2   | Architectural Details                                        | 67  |

|   |      | 3.2.3   | Key Performance Measures                                     | 67  |

|   |      | 3.2.4   | Application of Scheduling                                    | 68  |

|   |      | 3.2.5   | FPGA Implementation                                          | 71  |

|   | 3.3  | Novel   | Sparse OBC based Distributed Arithmetic Architecture for Ma- |     |

|   |      | trix T  | ransforms                                                    | 73  |

|   |      | 3.3.1   | Mathematical Background                                      | 74  |

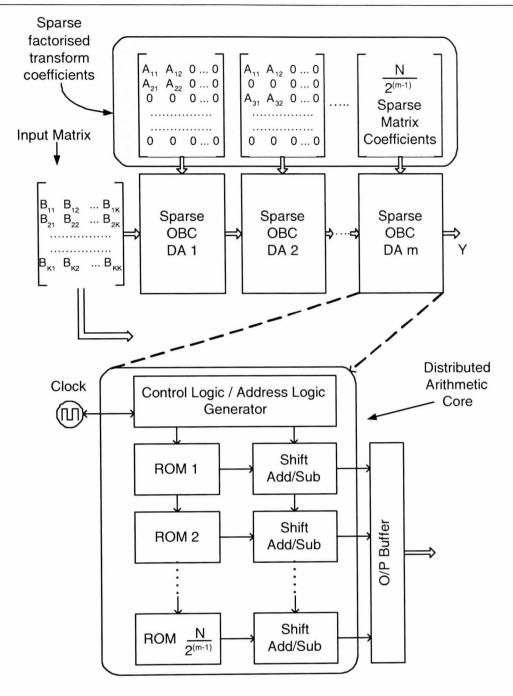

|   |      | 3.3.2   | Proposed Architecture and OBC-DA Operation                   | 76  |

|   |      | 3.3.3   | Implementation Details and Results Obtained                  | 78  |

|   |      | 3.3.4   | Power Analysis                                               | 79  |

|   | 3.4  | Efficie | ent FPGA Implementation of FHT for Signal Processing         | 80  |

|   |      | 3.4.1   | Mathematical Background                                      | 81  |

|   |      | 3.4.2   | Proposed Architecture for FHT - Design and Evaluation        | 85  |

|   |      | 3.4.3   | FPGA Implementation                                          | 88  |

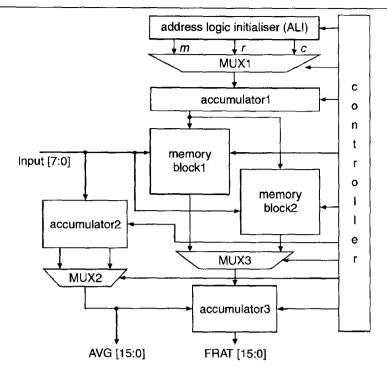

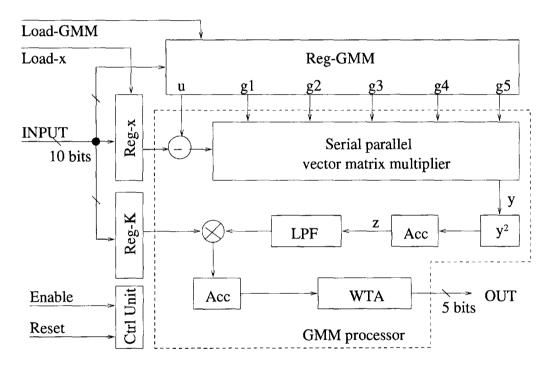

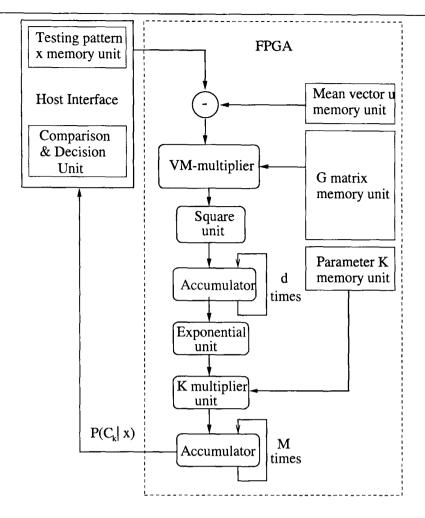

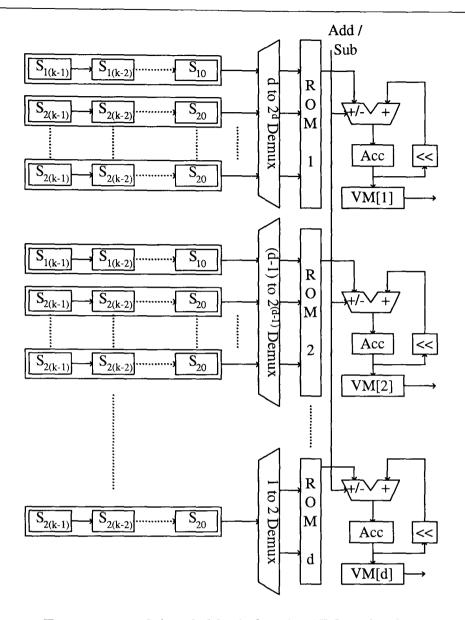

|   | 3.5  | Efficie | ent FPGA Implementation of GMM-Based Classifier Using DA.    | 93  |

|   |      | 3.5.1   | Algorithmic Review of GMM                                    | 94  |

|   |      | 3.5.2   | Architecture Description                                     | 95  |

|   |      | 3.5.3   | FPGA Implementation                                          | 99  |

|   | 3.6  | Concl   | usions                                                       | 100 |

| 4 | Arcl                 | chitectural Level Optimisation: Parallelism, Pipelining and Sys- |                                                                 |       |  |

|---|----------------------|------------------------------------------------------------------|-----------------------------------------------------------------|-------|--|

|   | tolis                | ation                                                            |                                                                 | 102   |  |

|   | 4.1                  | Introd                                                           | uction                                                          | . 102 |  |

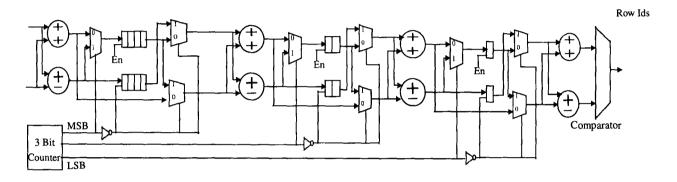

|   | 4.2                  | Accele                                                           | ration of Finite Radon Transform on Reconfigurable Hardware     | 103   |  |

|   |                      | 4.2.1                                                            | The Finite Radon Transform: A Brief Review                      | . 105 |  |

|   |                      | 4.2.2                                                            | Proposed Architectures for FRAT - Design and Evaluation .       | . 106 |  |

|   |                      | 4.2.3                                                            | FPGA Implementation                                             | . 111 |  |

|   | 4.3                  | Efficie                                                          | nt VLSI Architecture for the Finite Ridgelet Transform          | . 117 |  |

|   |                      | 4.3.1                                                            | Mathematical Background of the Finite Ridgelet Transform        | . 117 |  |

|   |                      | 4.3.2                                                            | Proposed Architectures for FRIT - Design and Evaluation .       | . 119 |  |

|   |                      | 4.3.3                                                            | Implementation Results and Metrics                              | . 122 |  |

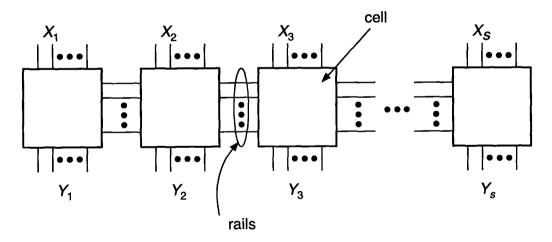

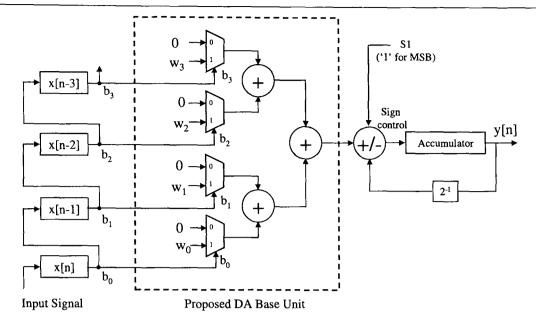

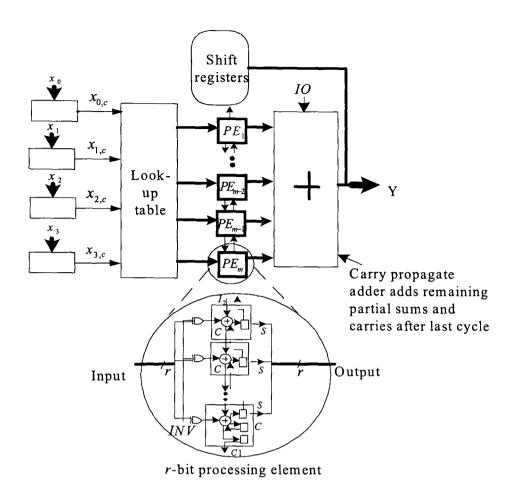

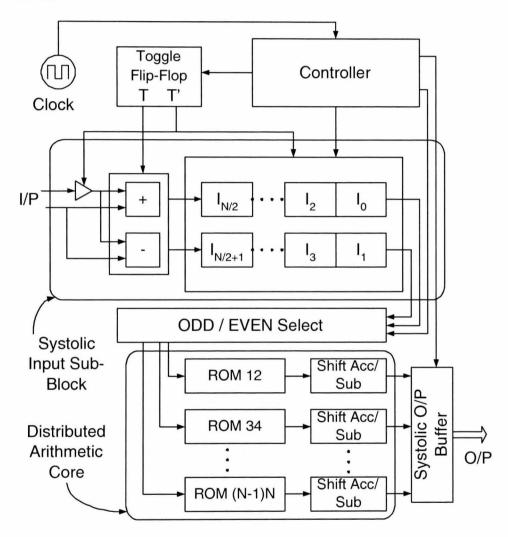

|   | 4.4                  | FPGA                                                             | Realisation of FIR Filters by Efficient and Flexible Systolisa- |       |  |

|   |                      | tion u                                                           | sing Distributed Arithmetic                                     | . 126 |  |

|   |                      | 4.4.1                                                            | Formulation of the Proposed Algorithm                           | . 128 |  |

|   |                      | 4.4.2                                                            | The Proposed Structures                                         | . 131 |  |

|   |                      | 4.4.3                                                            | Results and Discussions                                         | . 135 |  |

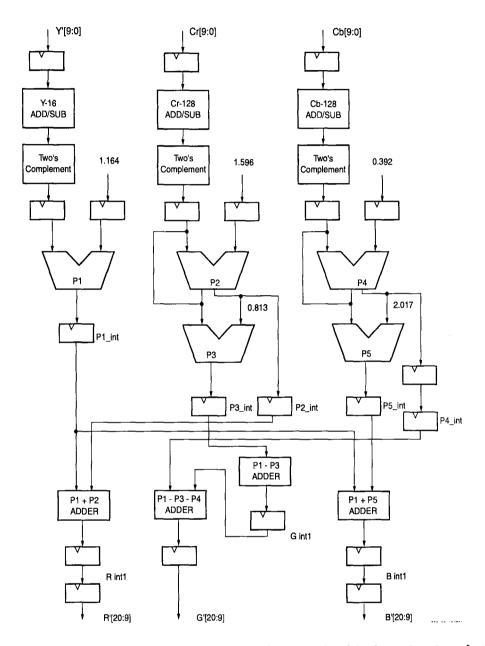

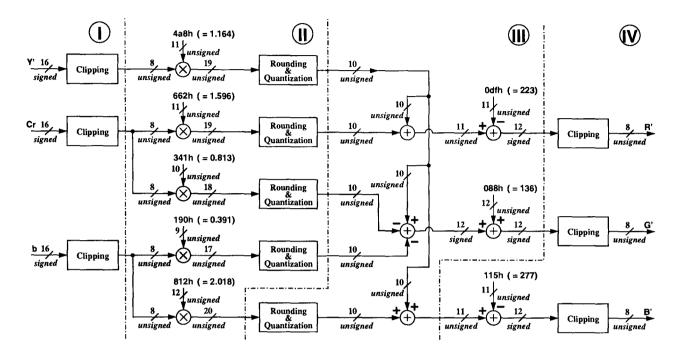

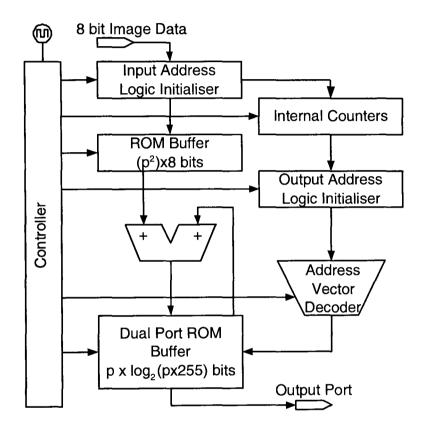

|   | 4.5                  | Efficie                                                          | ent FPGA Implementation of Colour Space Conversion              | . 142 |  |

|   |                      | 4.5.1                                                            | Mathematical Background                                         | . 142 |  |

|   |                      | 4.5.2                                                            | Proposed Architecture for CSC                                   | . 147 |  |

|   |                      | 4.5.3                                                            | FPGA Implementation                                             | . 149 |  |

|   | 4.6                  | Concl                                                            | usions                                                          | . 151 |  |

| 5 | $\operatorname{Per}$ | formaı                                                           | nce Enhanced Voltage Scaling in FPGAs                           | 153   |  |

|   | 5.1                  | Power                                                            | and Energy Dissipation: An FPGA perspective                     | . 154 |  |

|   |                      | 5.1.1                                                            | Power Dissipation Sources in Digital Circuits                   | . 154 |  |

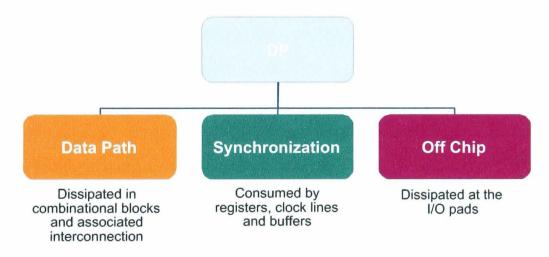

|   |                      | 5.1.2                                                            | Power Dissipation: FPGA Specific Details                        | . 155 |  |

|   | 5.2                  | FPGA                                                             | A Implementation: Empirical Study                               | . 157 |  |

|   |                      | 5.2.1                                                            | Description of Methodology                                      | . 157 |  |

|   |                      | 5.2.2                                                            | Description of the Benchmark Cores                              |       |  |

|   |                      | 5.2.3                                                            | FPGA Implementation Details                                     |       |  |

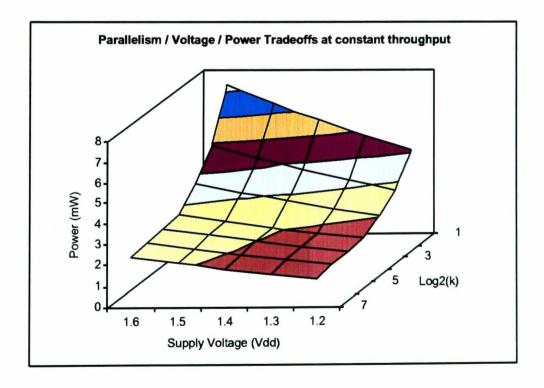

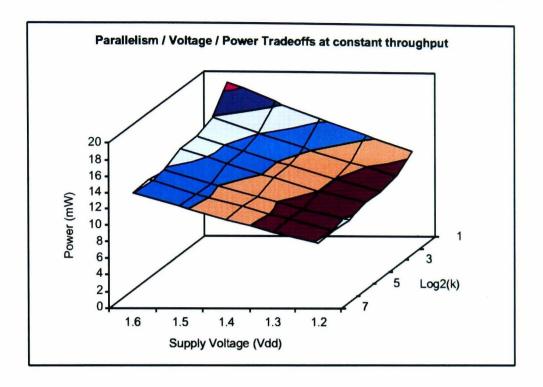

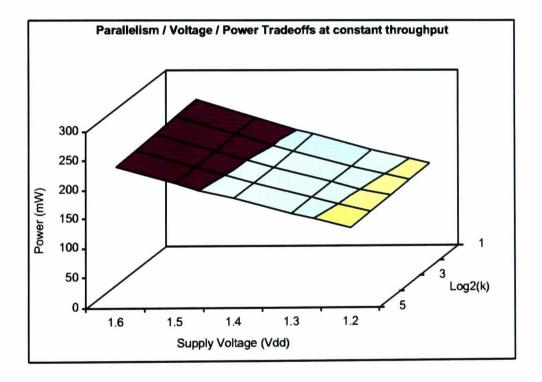

|   |                      | 5.2.4                                                            | Power/Parallelism/Voltage Tradeoffs                             | . 160 |  |

|   | 5.3                  | Concl                                                            | usions                                                          | . 162 |  |

Contents xv

| 6 | Fun                                 | ctional | Level Power Analysis and Modelling             | 163   |

|---|-------------------------------------|---------|------------------------------------------------|-------|

|   | 6.1                                 | Introdu | ction                                          | . 163 |

|   | 6.2                                 | FLPAN   | I: A Brief Introduction to Underlying Concepts | . 164 |

|   | 6.3                                 | Mathen  | natical Basis behind FLPAM                     | . 165 |

|   | 6.4                                 | FLPAN   | Applied to Various Cores                       | . 170 |

|   |                                     | 6.4.1   | Case Study I: Modelling the CSC Core           | . 171 |

|   |                                     | 6.4.2   | Case Study II: Modelling the FHT               | . 173 |

|   |                                     | 6.4.3   | Case Study III: Modelling the FRAT             | . 179 |

|   |                                     | 6.4.4   | Case Study IV: Modelling the FRIT              | . 186 |

|   | 6.5                                 | FLPAN   | M Evaluation                                   | . 193 |

|   | 6.6                                 | Conclu  | sion                                           | . 194 |

| 7 | Cor                                 | clusion | as and Future Work                             | 195   |

|   | 7.1                                 | Introdu | action                                         | . 195 |

|   | 7.2                                 | Evalua  | tion of Results and Contributions              | . 196 |

|   |                                     | 7.2.1   | Measurement of Success                         | . 196 |

|   |                                     | 7.2.2   | Important Novelty Claims                       | . 197 |

|   |                                     | 7.2.3   | Results Achieved                               | . 197 |

|   |                                     | 7.2.4   | Limitations                                    | . 199 |

|   | 7.3                                 | Future  | Work                                           | . 200 |

| В | ibliog                              | graphy  |                                                | 202   |

|   | $\mathbf{A}\mathbf{p}_{\mathbf{j}}$ | pendix  |                                                | ii    |

| A | Des                                 | sign En | try Tool Suite and Software Packages           | ii    |

|   | A.1                                 | Hande   | l-C                                            | . ii  |

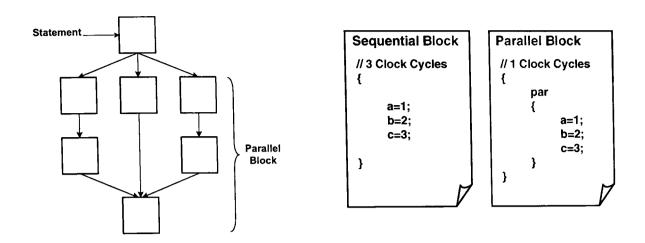

|   |                                     | A.1.1   | Parallel Hardware Generation                   | . v   |

|   |                                     | A.1.2   | Variables                                      | . v   |

|   |                                     | A.1.3   | Bit Level Operators                            | . vi  |

|   |                                     | A.1.4   | Channel Communications                         | . vi  |

|   |                                     | A.1.5   | Memory                                         | . vii |

|   |                                     | A.1.6   | External Communication                         | . ix  |

Contents xvi

|              | A.2 | Xilinx-                      | ISE                                                          | 3   | ix     |

|--------------|-----|------------------------------|--------------------------------------------------------------|-----|--------|

|              |     | A.2.1                        | Specifying Design Options                                    |     | ix     |

|              |     | A.2.2                        | Design Translation                                           | •   | ix     |

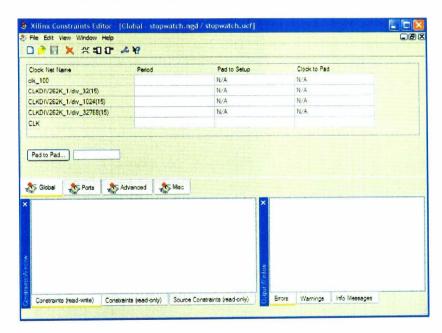

|              |     | A.2.3                        | Timing Constraints                                           |     | xi     |

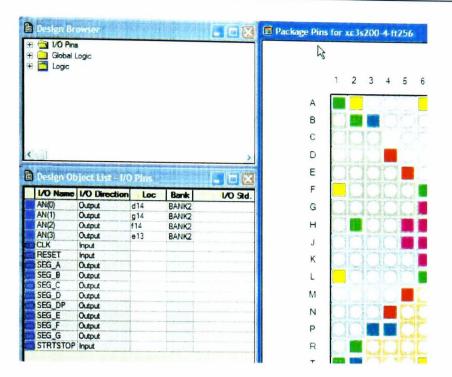

|              |     | A.2.4                        | Setting Pin and Location Constraints                         |     | xi     |

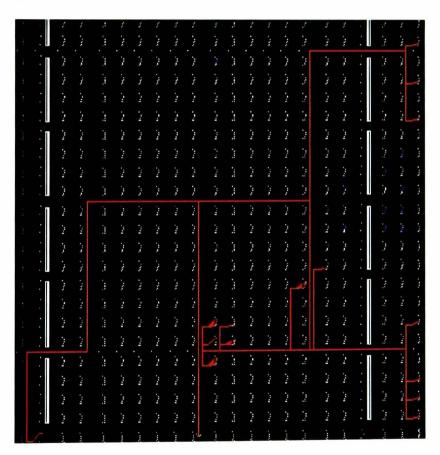

|              |     | A.2.5                        | Mapping, Place & Route                                       | . : | xii    |

|              |     | A.2.6                        | Verification of Place & Route                                | . : | xii    |

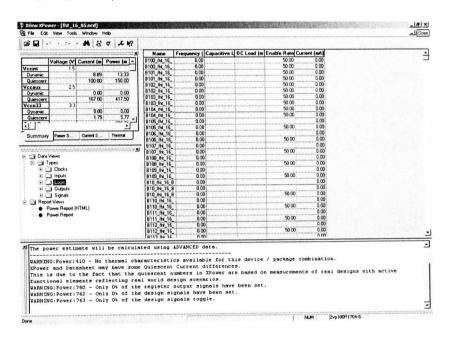

|              |     | A.2.7                        | Estimating and analysing Power using ISE XPower              | . > | civ    |

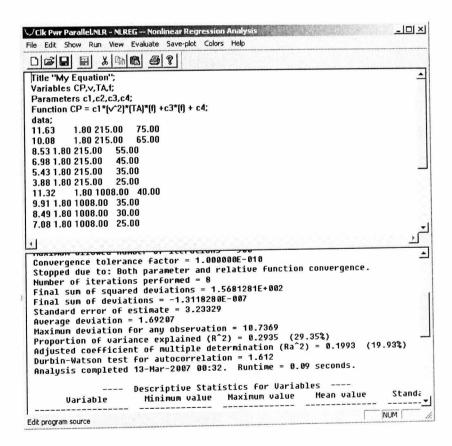

|              | A.3 | NLRE                         | G                                                            | . 3 | civ    |

| В            | Har | dware                        | Platforms for Synthesis & Implementation                     | x   | vi     |

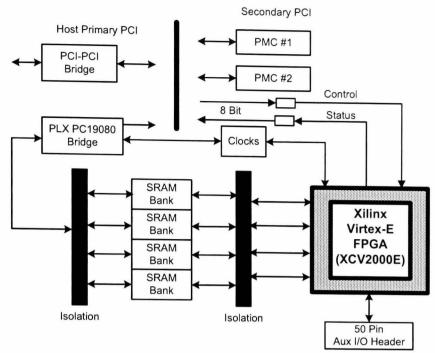

|              | B.1 | RC100                        | 00 Prototyping Platform                                      | . 3 | cvi    |

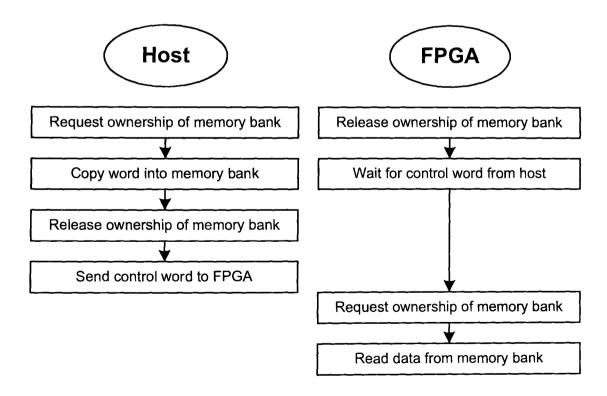

|              |     | B.1.1                        | Host-FPGA Communication                                      | . X | vii    |

|              | B.2 | FPGA                         | Devices Used in This Research                                | . 2 | kix    |

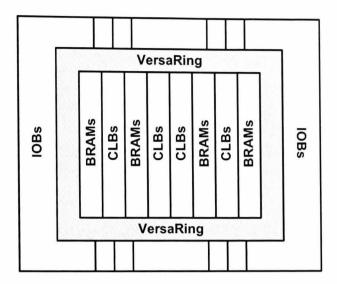

|              |     | B.2.1                        | Virtex-E FPGA                                                | . 2 | xix    |

|              |     | B.2.2                        | Virtex-II FPGA                                               | . х | xii    |

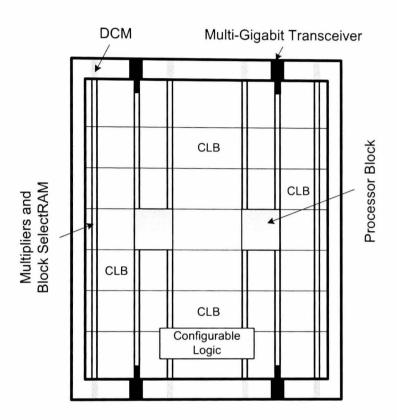

|              |     | B.2.3                        | Virtex-II Pro FPGA                                           | . х | xiv    |

|              |     | B.2.4                        | Spartan-3L FPGA                                              | . х | ΧV     |

|              |     | B.2.5                        | Virtex-4 FPGA                                                | . 3 | CXV    |

| $\mathbf{C}$ | Alg | orithn                       | ns and Arithmetic                                            | хх  | vii    |

|              | C.1 | The F                        | Finite Radon Transform and its Extension to other Higher Di- |     |        |

|              |     | mensi                        | onal Generalisations of Wavelets                             | . 3 | cxvii  |

|              |     | C.1.1                        | The Continuous Radon Transform                               | . 3 | cxvii  |

|              |     | C.1.2                        | The Finite Radon Transform and its Inverse- A Primer         | . 2 | xxviii |

|              |     | C.1.3                        | Ridgelets and Curvelets                                      | . 3 | xxxi   |

|              | C.2 | Colou                        | r Spaces and Conversion Formulae                             | . 3 | xxxi   |

|              | C.3 | Distri                       | buted Arithmetic                                             | . : | xxxiii |

|              |     | C.3.1                        | Suitability of DA for FPGAs                                  | . : | xxxiii |

|              |     | C.3.2                        | Mathematical Formulation of DA                               | . : | xxxiii |

|              | C A | $\mathbf{p} \cap \mathbf{M}$ | Size Reduction in DA                                         |     | xxxiv  |

| Contents    | • •  |

|-------------|------|

| Contonts    | XVII |

| k ADHILEHUS | XVII |

|             |      |

| D | Various Compound Energy Cost Functions |                                       |  |         |  |  |  |  |  |

|---|----------------------------------------|---------------------------------------|--|---------|--|--|--|--|--|

|   | D.1                                    | Energy per Operation                  |  | xxxvi   |  |  |  |  |  |

|   | D.2                                    | Energy Area                           |  | xxxvii  |  |  |  |  |  |

|   | D.3                                    | Energy Throughput                     |  | xxxvii  |  |  |  |  |  |

|   | D.4                                    | Energy Per Pixel and Energy Per Frame |  | xxxviii |  |  |  |  |  |

# List of Figures

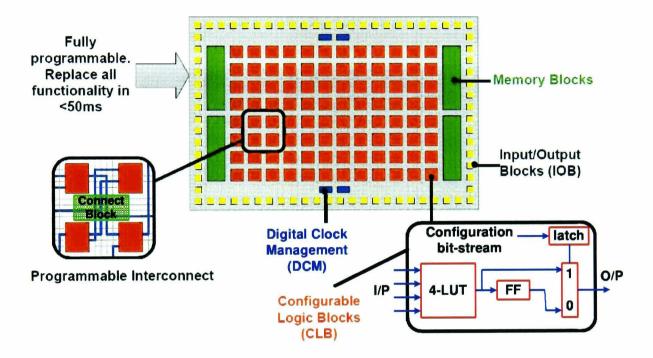

| 1.1  | Generic FPGA structure showing internal blocks                        | 6  |

|------|-----------------------------------------------------------------------|----|

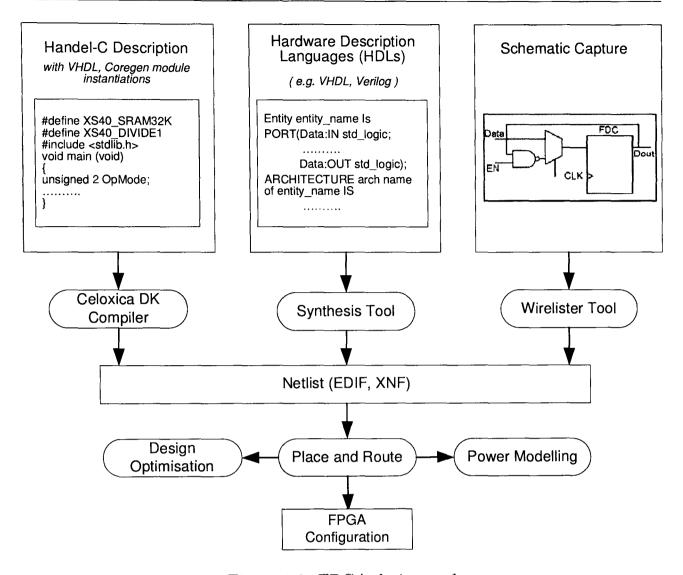

| 1.2  | FPGA design cycle                                                     | 8  |

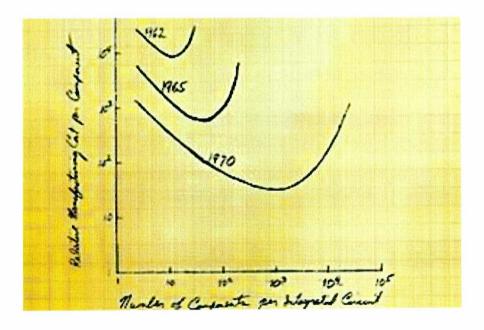

| 1.3  | Gordon Moore's original graph from 1965. Courtesy Intel               | 11 |

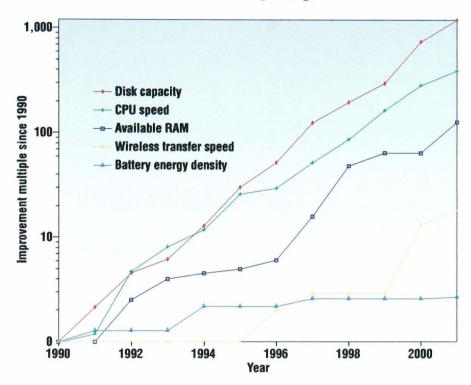

| 1.4  | Battery capacity growth in comparison to other related technology     |    |

|      | trends                                                                | 12 |

| 1.5  | Electronic Nose Prototype                                             | 13 |

| 1.6  | Dynamic power dissipation on FPGAs                                    | 14 |

| 1.7  | Various abstraction levels at which power reduction strategies can be |    |

|      | applied                                                               | 18 |

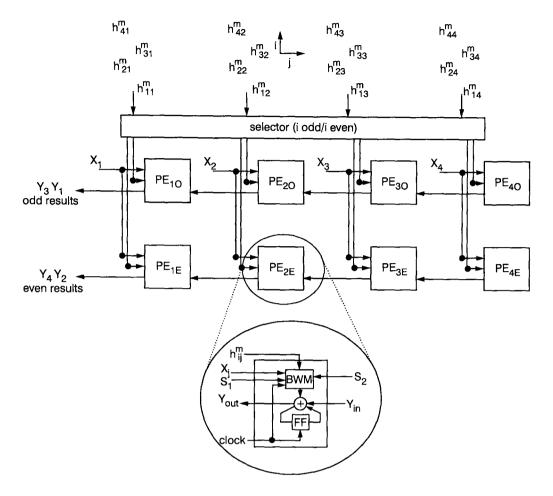

| 2.1  | BWM based systolic architecture [16]                                  | 25 |

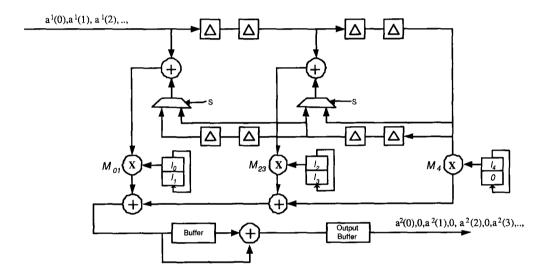

| 2.2  | DA based architecture for the W-H transform [16]                      | 26 |

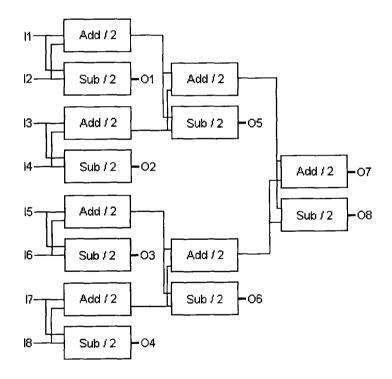

| 2.3  | Butterfly architecture for 4 stage WHT for the case $N=16$ [27]       | 27 |

| 2.4  | Basic LUT cascade [29]                                                | 28 |

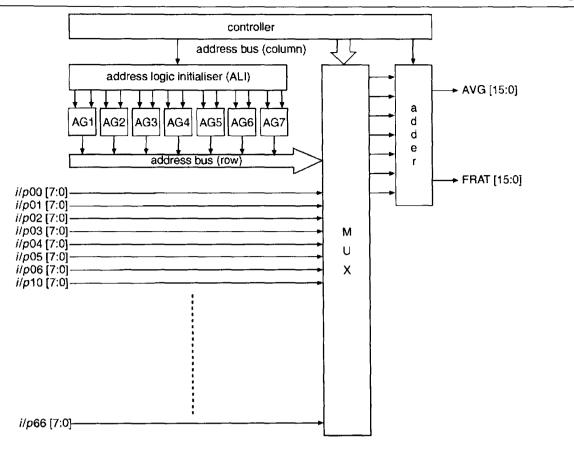

| 2.5  | Reference architecture for the FRAT [34]                              | 30 |

| 2.6  | Memoryless architecture for the FRAT [34]                             | 31 |

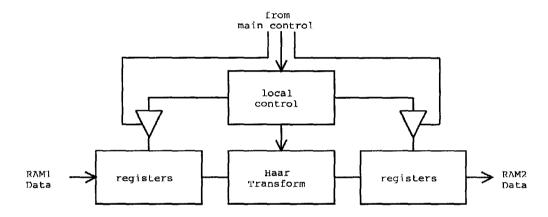

| 2.7  | Generic architecture for the FRAT [37]                                | 32 |

| 2.8  | Generic tree-based architecture for the DWT [37]                      | 32 |

| 2.9  | Standard pseudocode based architecture for the FRAT [37]              | 33 |

| 2.10 | DWT sub-block for the standard pseudocode based FRIT architecture     |    |

|      | [37]                                                                  | 33 |

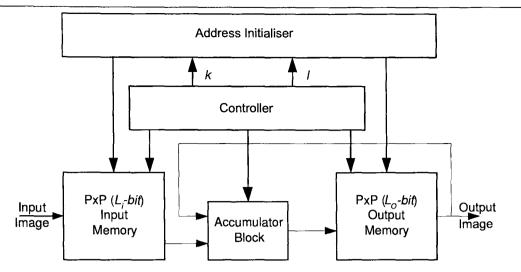

| 2.11 | Standard pseudocode based architecture for the FRAT [21]              | 34 |

| 2.12 | DBWT sub-block based on the àtrous algorithm [21]                     | 34 |

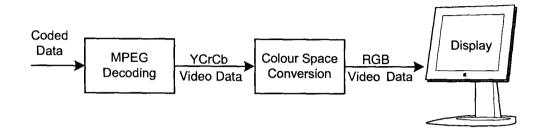

| 2.13 | The video decoding process                                            | 35 |

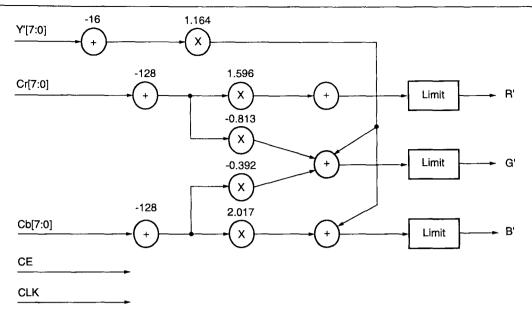

| 2.14 | Simple arithmetic architecture for CSC [40]                                    | 36 |

|------|--------------------------------------------------------------------------------|----|

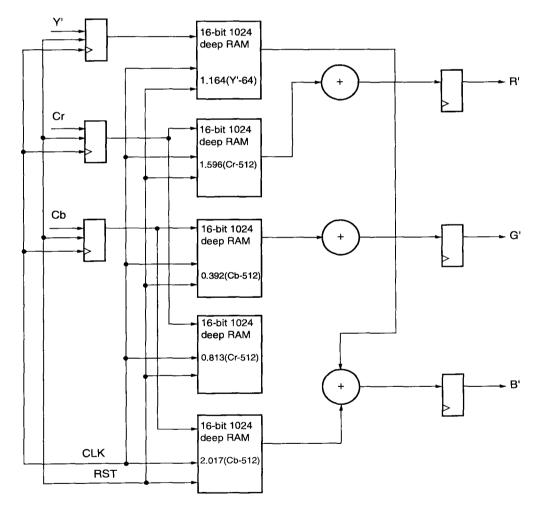

| 2.15 | LUT based CSC architecture [40]                                                | 36 |

| 2.16 | CSC architecture based on embedded multiplier [40]                             | 37 |

| 2.17 | Four stage YCrCb to RGB FPGA Trimedia co-processor [41]                        | 38 |

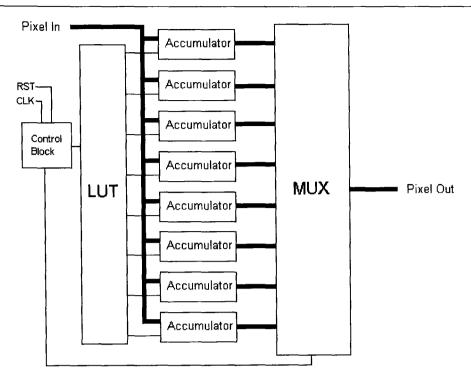

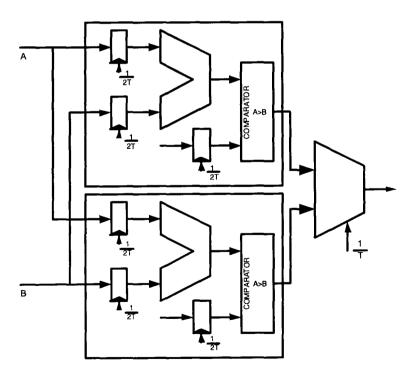

| 2.18 | Functional units in the GMM classifier [47]                                    | 40 |

| 2.19 | LUT-less OBC DA architecture for 4-tap FIR filter [54]                         | 42 |

| 2.20 | r-bit serial DA one-LUT design for a four-product MAC [56]                     | 43 |

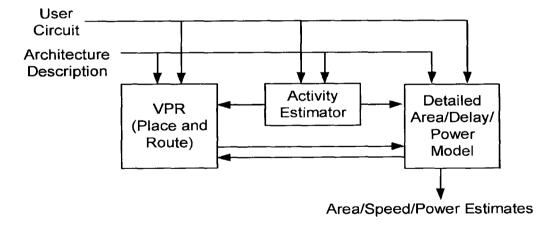

| 2.21 | Modified VPR framework used for power modelling [61, 62]                       | 44 |

| 2.22 | Real-time cycle accurate measurement system for SRAM FPGAs                     |    |

|      | [64, 65]                                                                       | 46 |

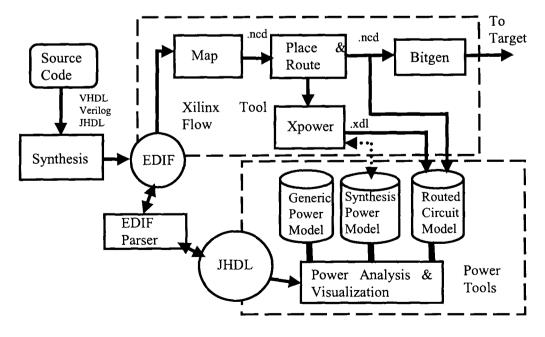

| 2.23 | High level power macromodelling for reconfigurable hardware [66]               | 47 |

| 2.24 | Macro-model characterisation procedure [67]                                    | 48 |

| 2.25 | High level FPGA power estimation methodology [68]                              | 49 |

| 2.26 | High level FPGA power estimation methodology [69]                              | 49 |

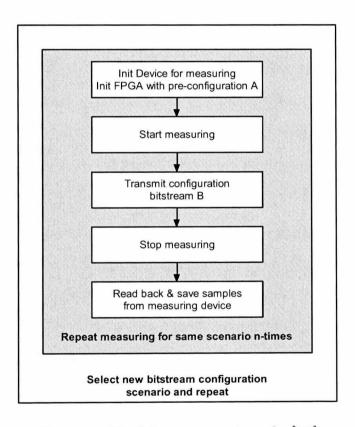

| 2.27 | Measurement cycle [71]                                                         | 50 |

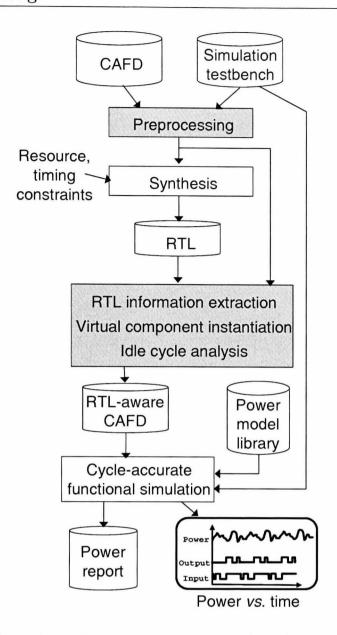

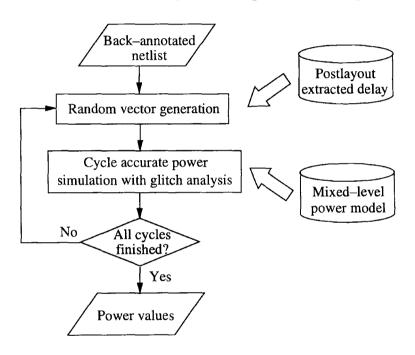

| 2.28 | Overview of the CAFD power estimation methodology [72]                         | 52 |

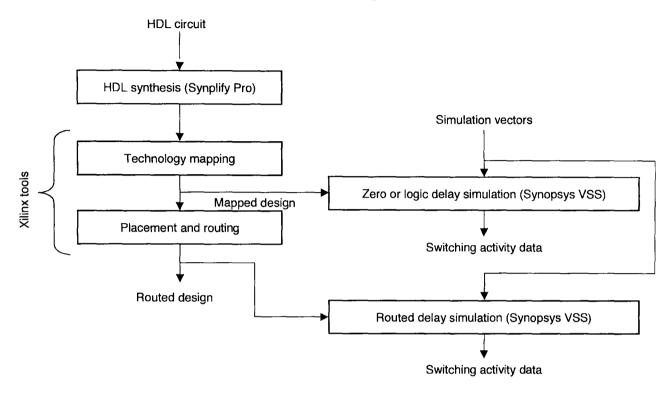

| 2.29 | CAD flow for activity analysis [73]                                            | 53 |

| 2.30 | Overall power calculation [74]                                                 | 54 |

| 2.31 | Parallel implementation of a simple datapath [102]                             | 58 |

| 3.1  | Architectural block diagram                                                    | 67 |

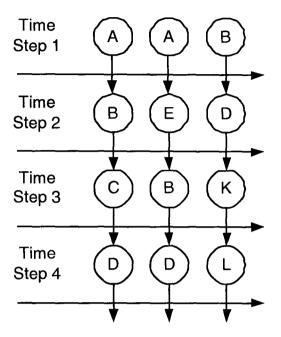

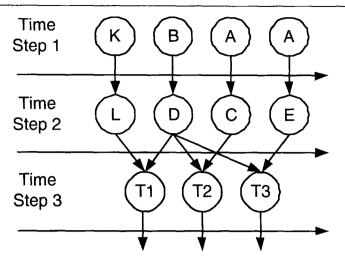

| 3.2  | Unscheduled dataflow                                                           | 69 |

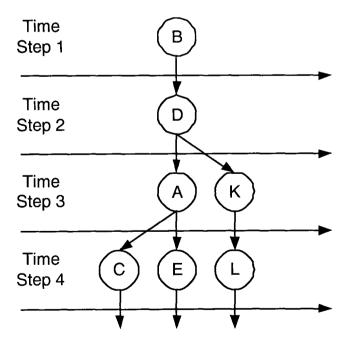

| 3.3  | Latency optimised scheduling                                                   | 70 |

| 3.4  | Area optimised scheduling                                                      | 70 |

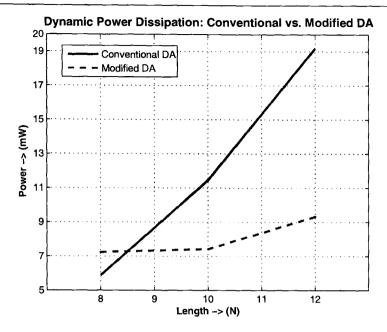

| 3.5  | Comparison of dynamic power consumption                                        | 73 |

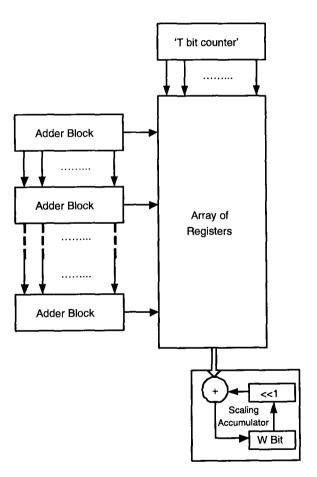

| 3.6  | Block diagram of the overall OBC-DA-sparse matrix based DOT im-                |    |

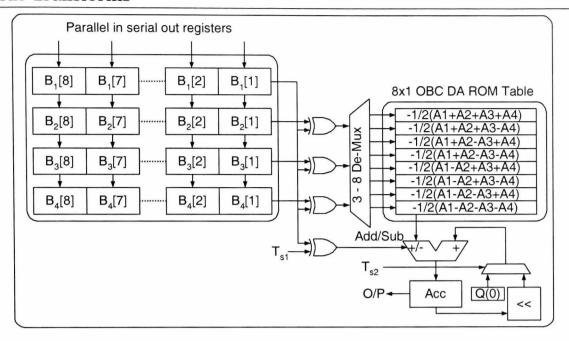

|      | plementation                                                                   | 77 |

| 3.7  | Architecture for the OBC-DA block for the case ${\cal N}=4$ and ${\cal W}=8$ . | 78 |

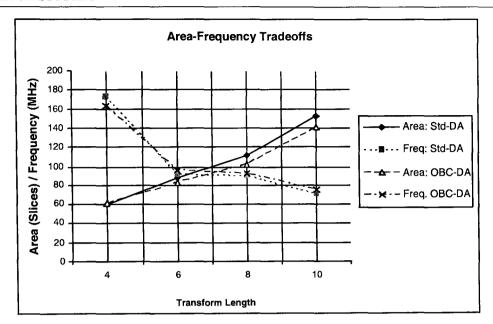

| 3.8  | Frequency-Area trends for both architectures for different values of $N$       |    |

|      | and $W = 8$ . Frequency is in MHz and area is represented in FPGA              |    |

|      | slices                                                                         | 79 |

| 3.9  | Total dynamic power dissipation for different values of $N$ and $W=8$ .        | 80 |

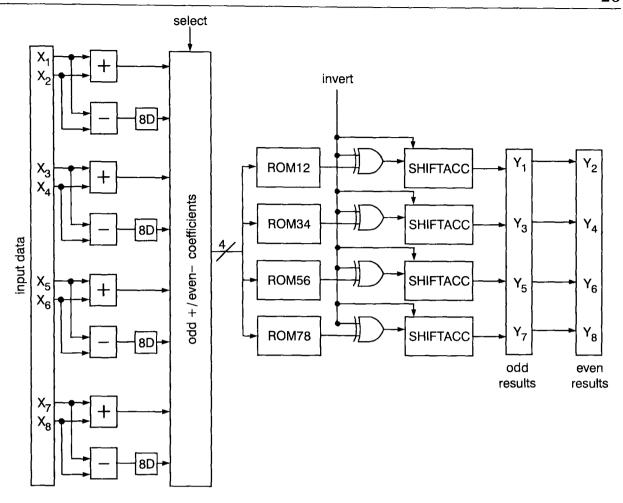

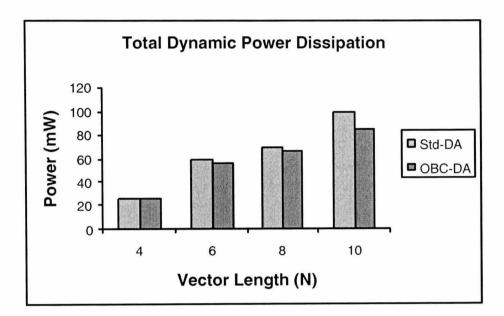

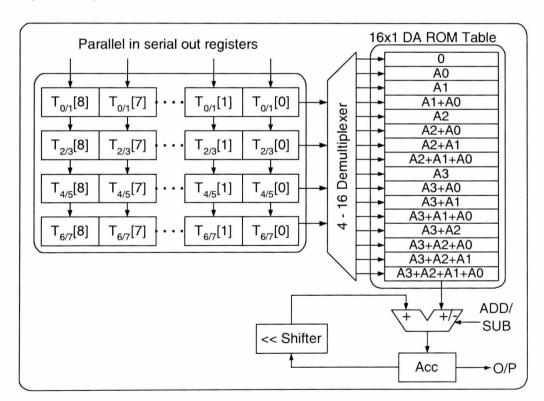

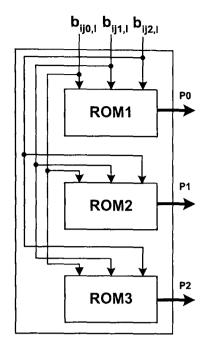

| 3.10 | Novel DA based architecture for FHT                                                                                                                              |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

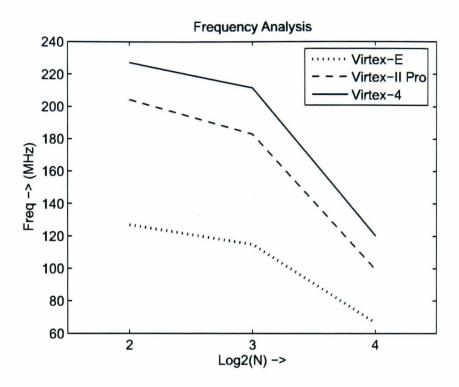

| 3.11 | DA module structure and ROM contents for $N=8, W=8$                                                                                                              |

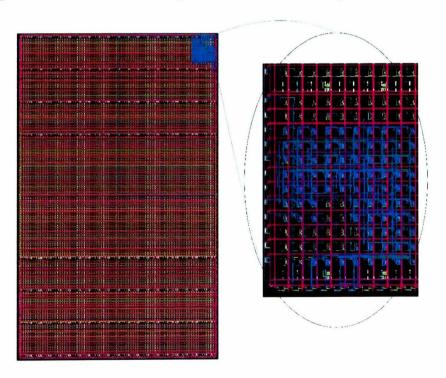

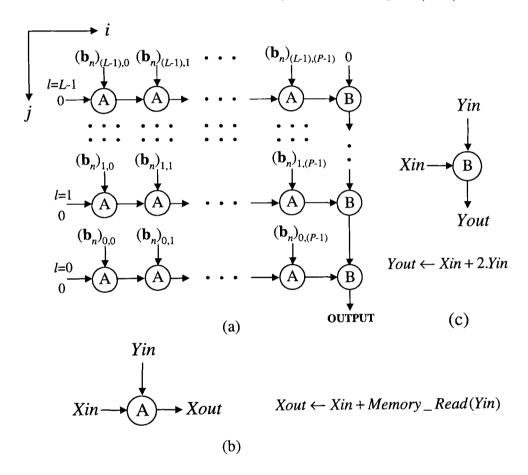

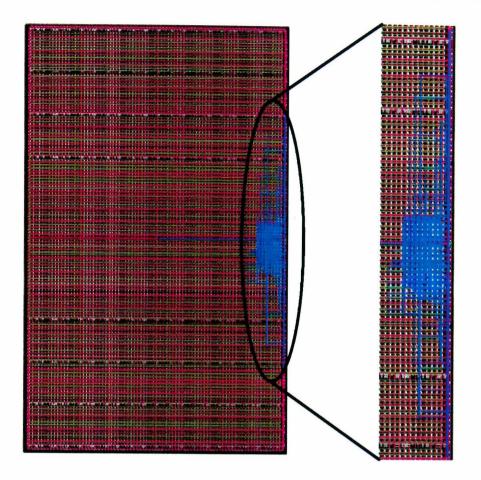

| 3.12 | Maximum frequency obtained for all platforms: $N = 4, 8, 16 \dots 91$                                                                                            |

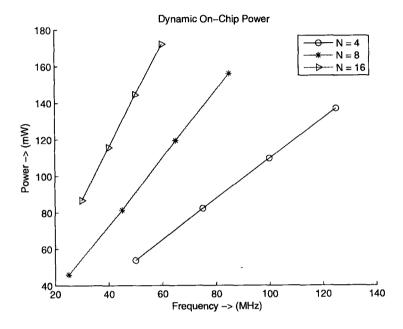

| 3.13 | Chip diagram showing manual placement, routing and pin assign-                                                                                                   |

|      | ment; Virtex-E XCV2000E FPGA                                                                                                                                     |

| 3.14 | Dynamic power dissipation for the FHT core                                                                                                                       |

| 3.15 | Data flow block diagram of GMM classifier. Memory units are used                                                                                                 |

|      | to store various GMM coefficients such as $K, G$ and $\mu \dots 97$                                                                                              |

| 3.16 | DA sub-block for the VM-multiplier                                                                                                                               |

| 3.17 | Chip diagram showing manual placement, routing and pin assign-                                                                                                   |

|      | ment; Virtex-E XCV2000E FPGA                                                                                                                                     |

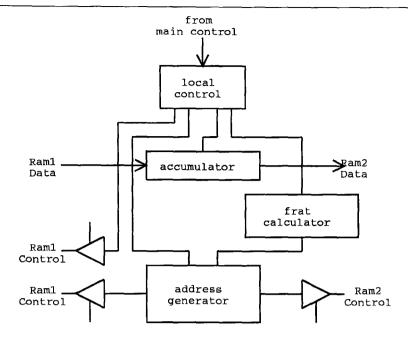

| 4.1  | Reference architecture for the FRAT                                                                                                                              |

| 4.2  | FRAT architecture with parallel core                                                                                                                             |

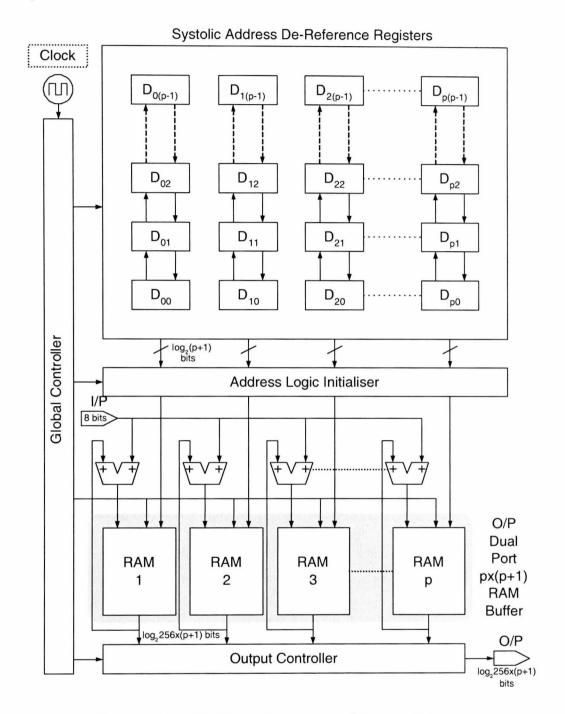

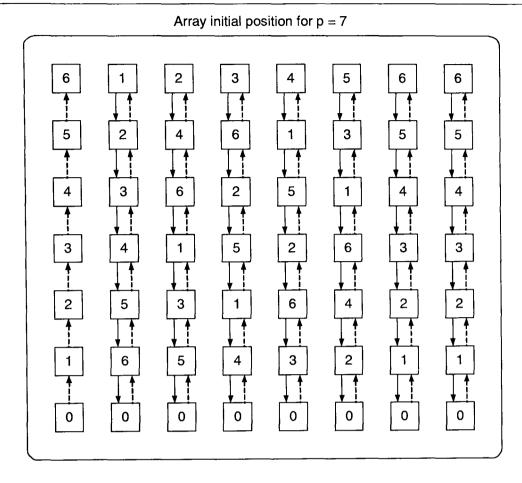

| 4.3  | Initial array register contents for the case $p = 7 \dots \dots$ |

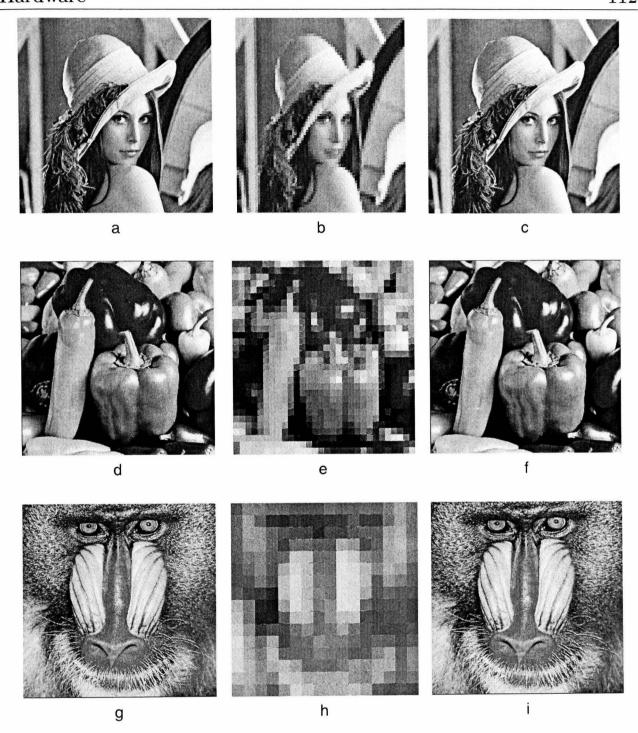

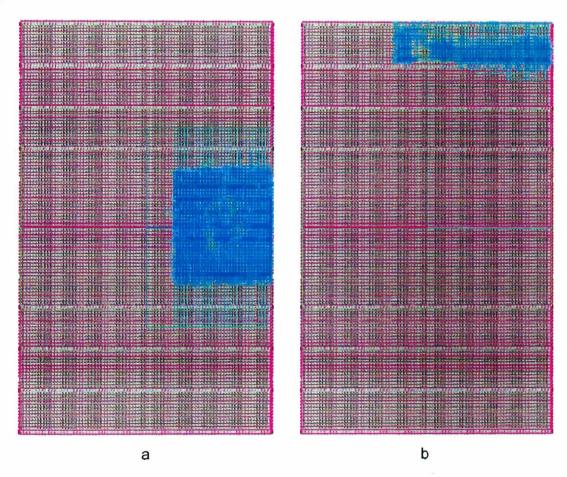

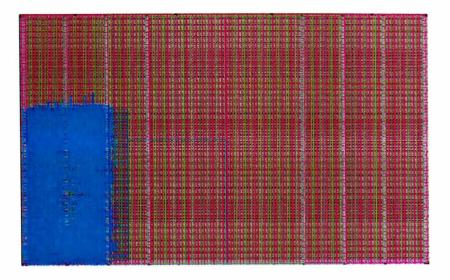

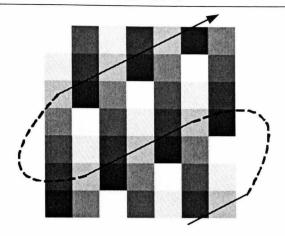

| 4.4  | Spatial domain and transformed images (a) Spatial Domain Lena (b)                                                                                                |

|      | FRAT domain, $p = 7$ (c) Reconstructed Image (d) Spatial Domain                                                                                                  |

|      | Peppers (e) FRAT domain, $p = 17$ (f) Reconstructed Image (g) Spa-                                                                                               |

|      | tial Domain Baboon (h) FRAT domain, $p = 31$ (i) Reconstructed                                                                                                   |

|      | Image                                                                                                                                                            |

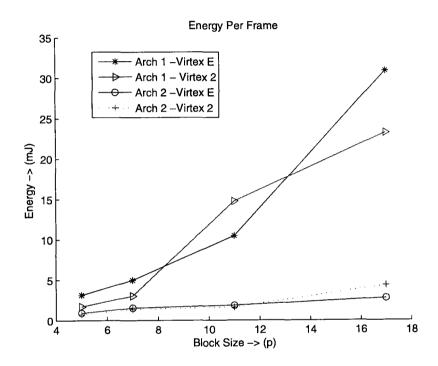

| 4.5  | Comparison of EPF for the "reference" and proposed parallel FRAT                                                                                                 |

|      | architectures                                                                                                                                                    |

| 4.6  | Chip diagrams for $p=31$ (a) Parallel architecture (b) Reference                                                                                                 |

|      | architecture; (Virtex-E XCV2000E FPGA)                                                                                                                           |

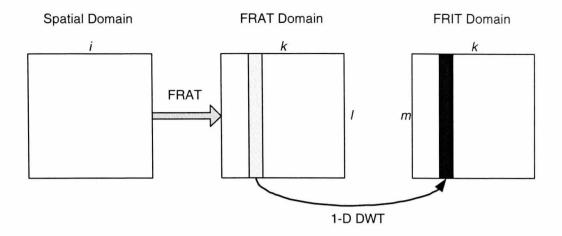

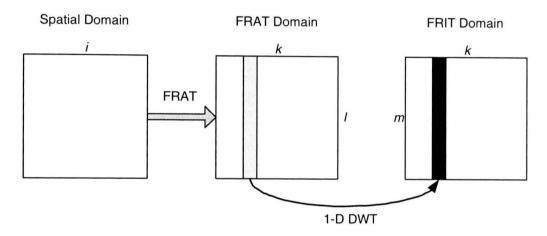

| 4.7  | Finite Ridgelet transform obtained by performing DWT on the FRAT                                                                                                 |

|      | vectors                                                                                                                                                          |

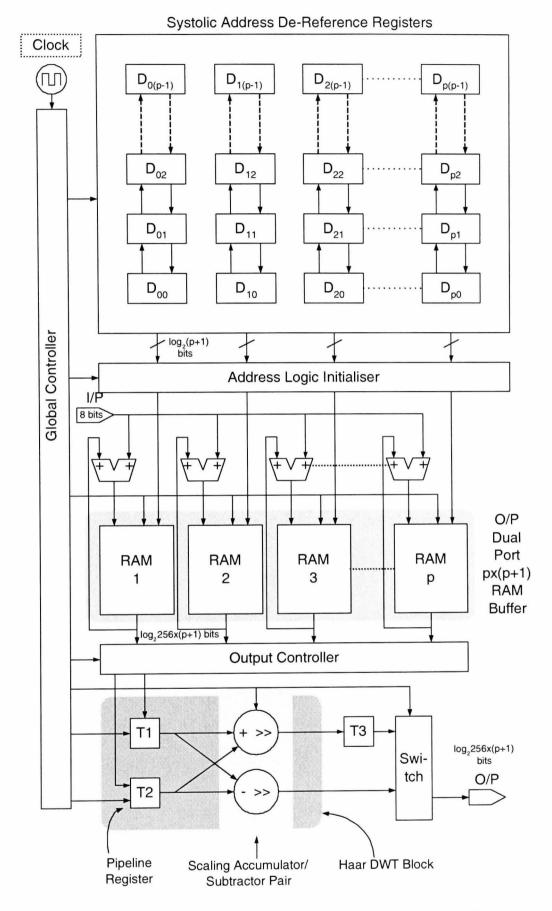

| 4.8  | FRIT architecture with the FRAT and Haar DWT sub-blocks 120                                                                                                      |

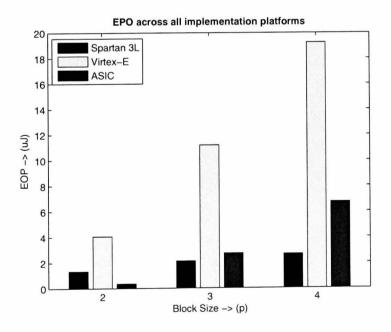

| 4.9  | Comparison of EOP across different platforms                                                                                                                     |

| 4.10 | Chip diagram for the case $p=31$ implemented on the Virtex-E                                                                                                     |

|      | XCV2000E FPGA                                                                                                                                                    |

| 4.11 | Chip layout for ASIC implementation for the case $p=31$ 125                                                                                                      |

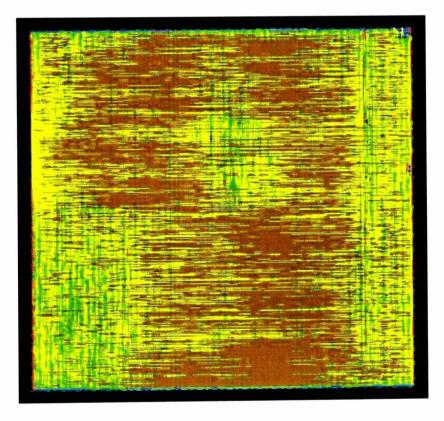

| 4.12 | Spatial domain and transformed images (a) Spatial domain Lena (b)                                                |

|------|------------------------------------------------------------------------------------------------------------------|

|      | FRIT domain, $p=7$ (c) Spatial domain Peppers (d) Reconstructed                                                  |

|      | image (e) Spatial domain Baboon (f) FRIT domain, $p=31 \ldots 127$                                               |

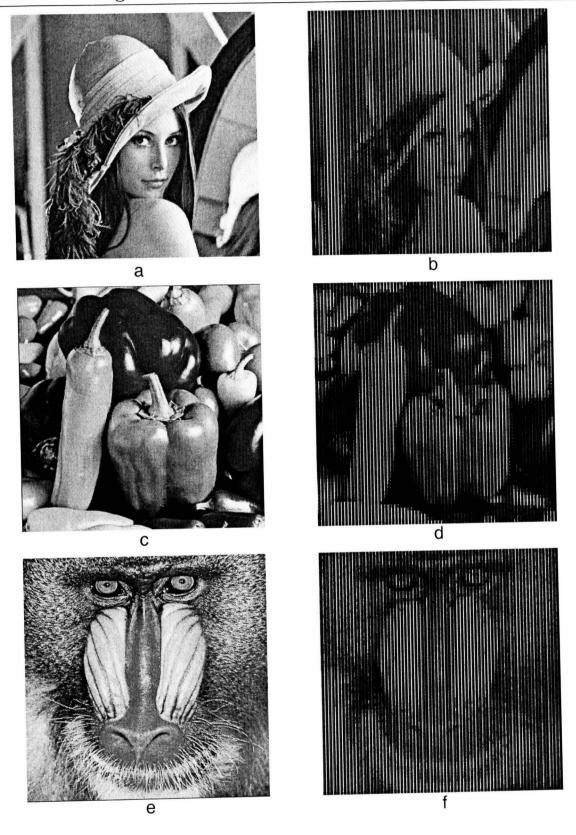

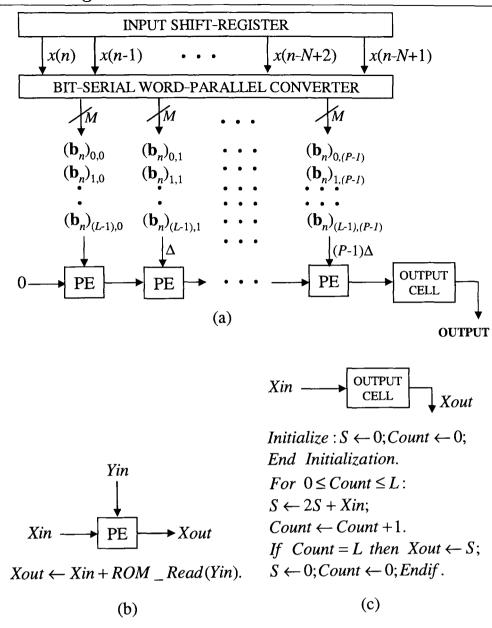

| 4.13 | The DG for DA-based implementation of FIR filter. (a) The DG. (b)                                                |

|      | Function of node A. (c) Function of node B                                                                       |

| 4.14 | The proposed 1-D array for DA-based implementation of FIR filter.                                                |

|      | (a) The linear systolic array. (b) Function of PE. (c) Function of                                               |

|      | output cell. $\Delta$ stands for a unit delay                                                                    |

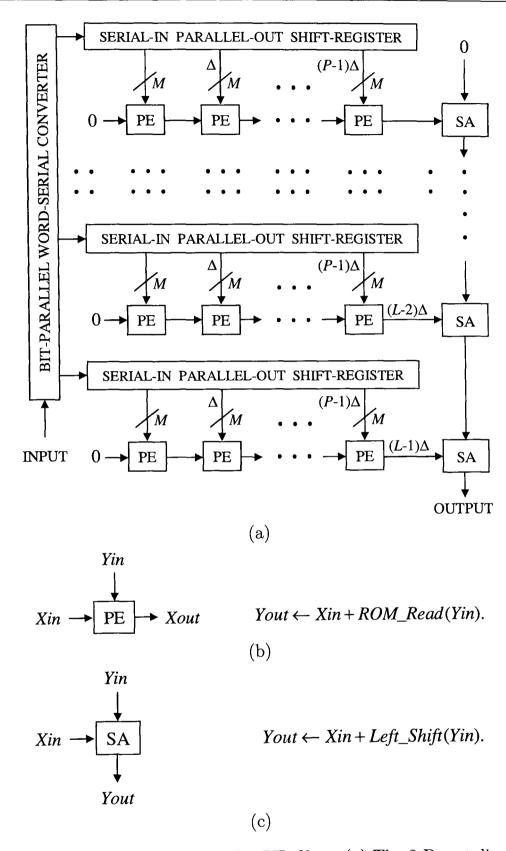

| 4.15 | The proposed 2-D array for FIR filter. (a) The 2-D systolic array.                                               |

|      | (b) Function of PE. (c) Function of SA cell. $\Delta$ stands for unit delay 134                                  |

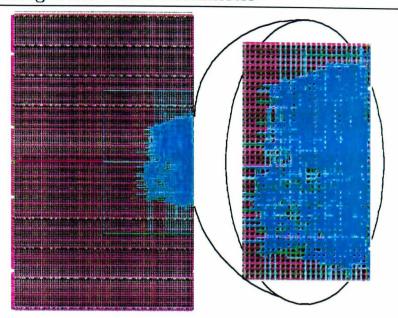

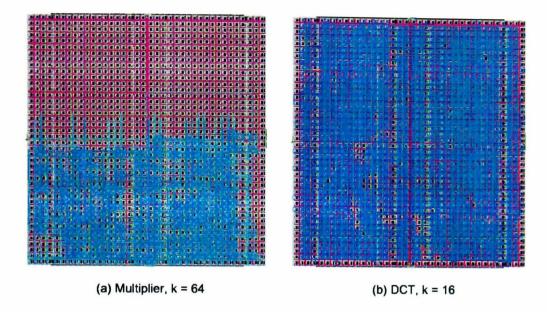

| 4.16 | FPGA chip diagram for FIR filter realisation for $N=64,M=8$ and                                                  |

|      | $L=8 \; ({\rm Xilinx} \; {\rm XCV2000E} \; {\rm FPGA}) \; \ldots \; \ldots \; \ldots \; \ldots \; \ldots \; 139$ |

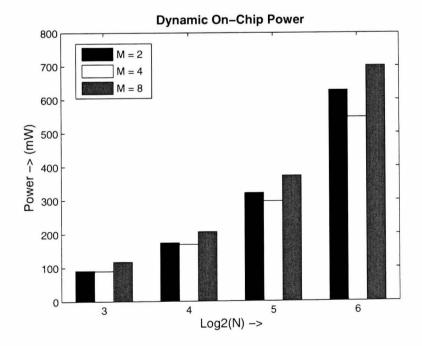

| 4.17 | Plot of variation of dynamic on-chip power with filter order 140                                                 |

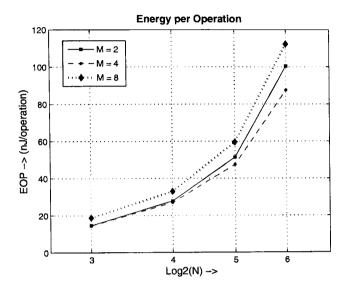

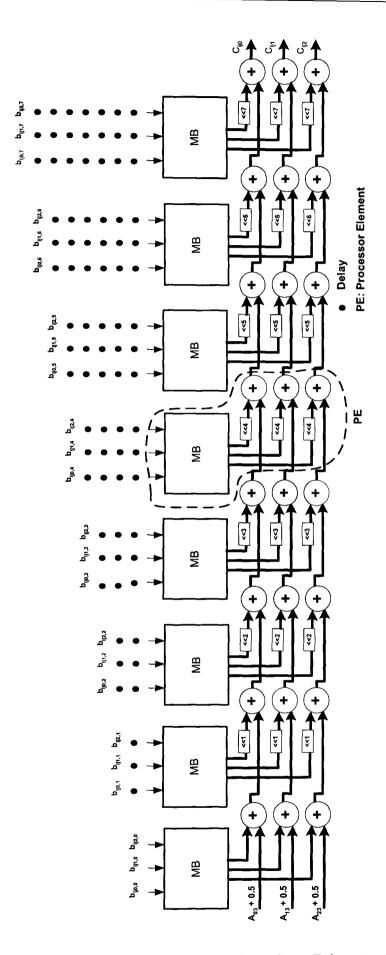

| 4.18 | Energy per operation of FPGA implementations FIR filter for differ-                                              |

|      | ent values of $N$ and $M$                                                                                        |

| 4.19 | Energy throughput of FPGA implementations for different values of                                                |

|      | N and $M$                                                                                                        |

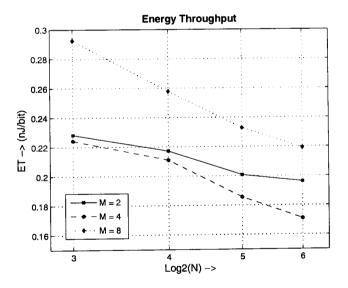

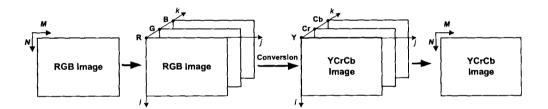

| 4.20 | RGB to YCrCb conversion                                                                                          |

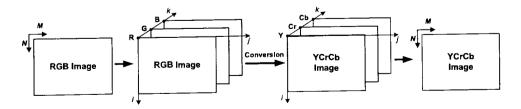

| 4.21 | Proposed architecture based on DA principles                                                                     |

| 4.22 | MB structure                                                                                                     |

| 4.23 | Design layout for the proposed architecture (XCV2000E FPGA) $151$                                                |

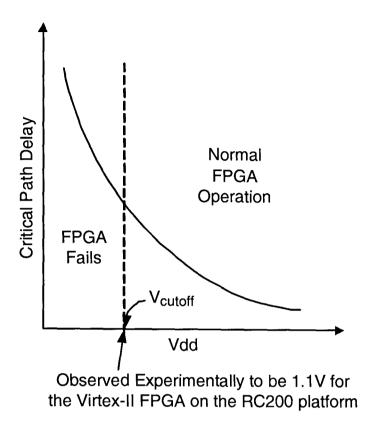

| 5.1  | Delay vs supply voltage tradeoff trends and FPGA operational con-                                                |

|      | ditions                                                                                                          |

| 5.2  |                                                                                                                  |

|      | FPGA)                                                                                                            |

| 5.3  | Power/Parallelism/Voltage tradeoff for the adder core                                                            |

| 5.4  | Power/Parallelism/Voltage tradeoff for the multiplier core 161                                                   |

| 5.5  | Power/Parallelism/Voltage tradeoff for the DCT core                                                              |

| 6.1  | Proposed design flow for FLPAM based power and energy optimised                                                  |

|      | design of FPGA cores                                                                                             |

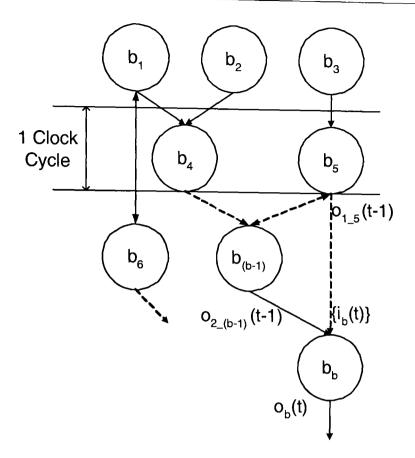

| 6.2  | A generic Data Flow Graph indicating all parameters                  |

|------|----------------------------------------------------------------------|

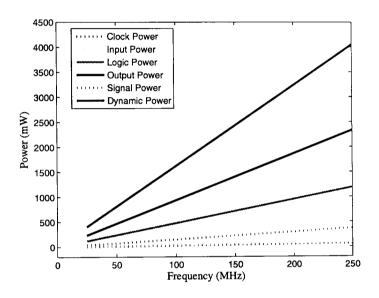

| 6.3  | CSC Power diagram                                                    |

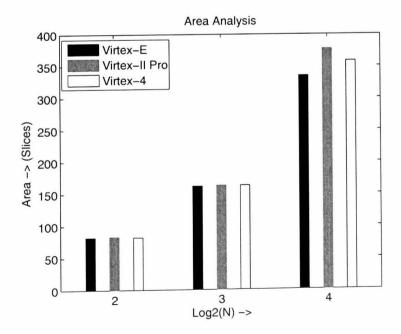

| 6.4  | Area occupied for different transform lengths : $N=4,8,16\ldots 174$ |

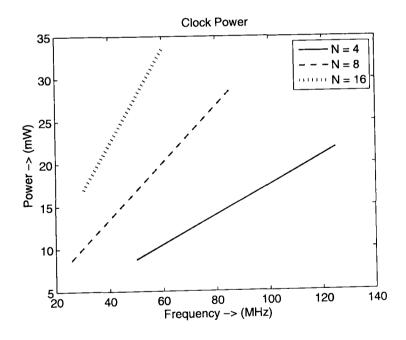

| 6.5  | CP for $N=4,8,16$ at different frequencies                           |

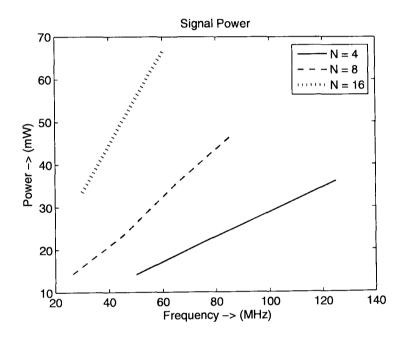

| 6.6  | SP for $N = 4, 8, 16$ at different frequencies $.'$                  |

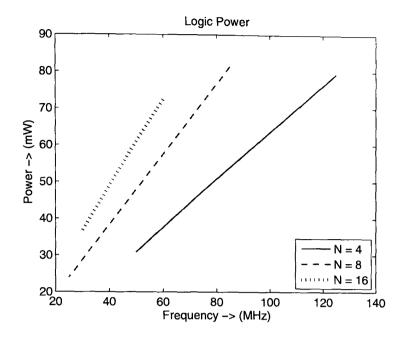

| 6.7  | LP for $N=4,8,16$ at different frequencies                           |

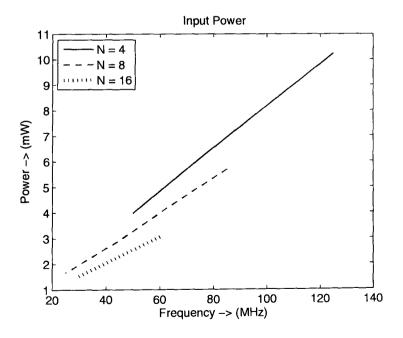

| 6.8  | IpP for $N=4,8,16$ at different frequencies                          |

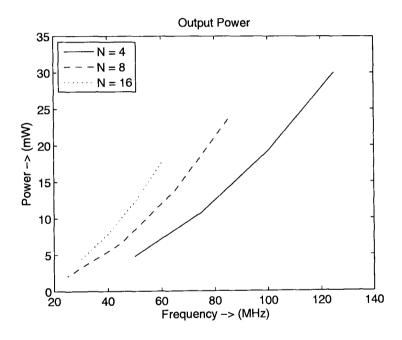

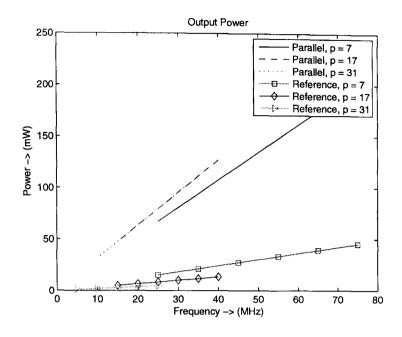

| 6.9  | OP for $N=4,8,16$ at different frequencies                           |

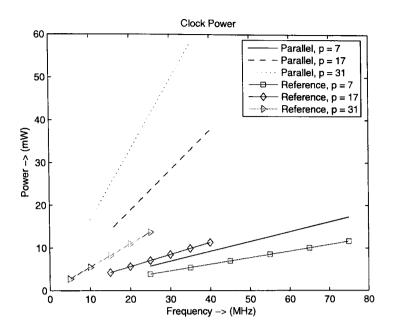

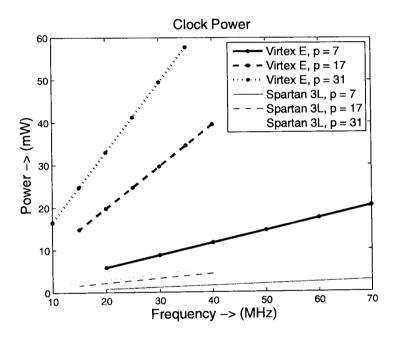

| 6.10 | CP chart for the FRAT core                                           |

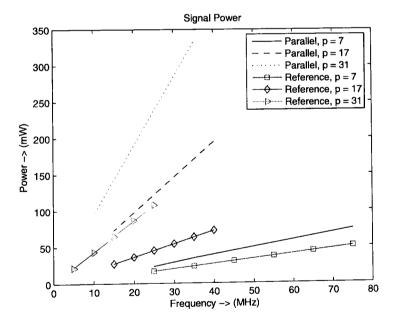

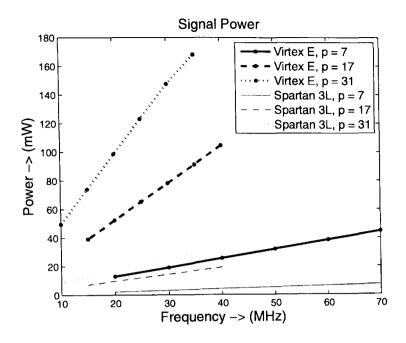

| 6.11 | SP chart for the FRAT core                                           |

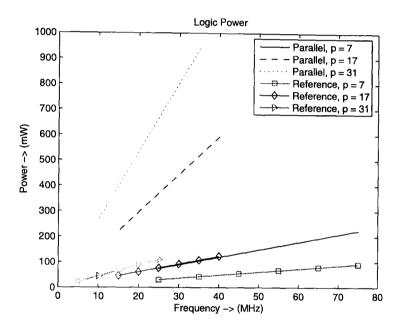

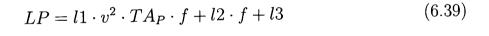

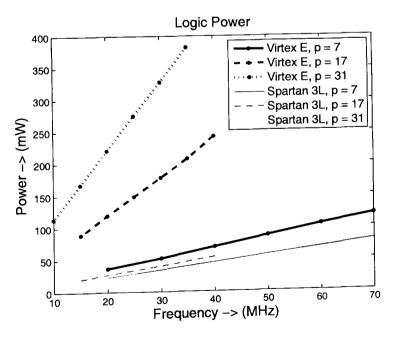

| 6.12 | LP chart for the FRAT core                                           |

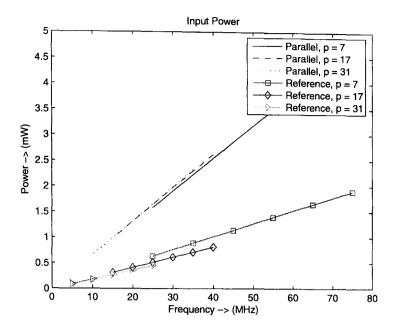

| 6.13 | IpP chart for the FRAT core                                          |

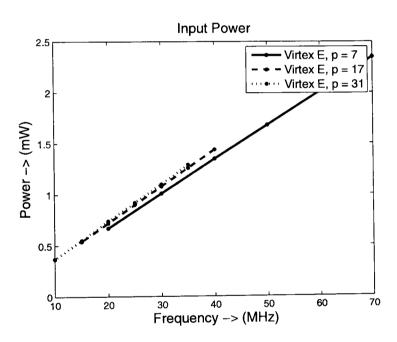

| 6.14 | OP chart for the FRAT core                                           |

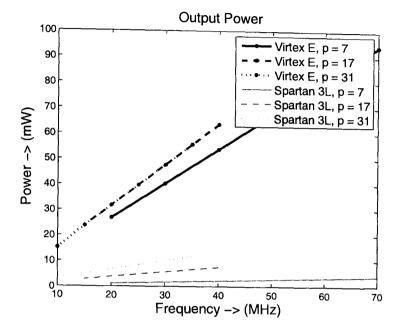

| 6.15 | CP chart for the FRIT core                                           |

| 6.16 | SP chart for the FRIT core                                           |

| 6.17 | LP chart for the FRIT core                                           |

| 6.18 | IpP chart for the FRIT core                                          |

| 6.19 | OP chart for the FRIT core                                           |

| 6.20 | ASIC SP chart for the FRIT core                                      |

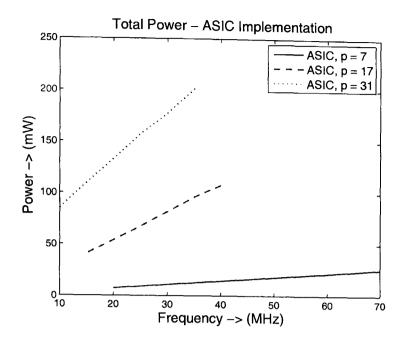

| A.1  | The DK design synthesis tool for entering Handel-C code iii          |

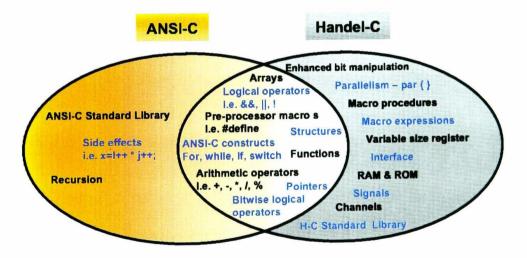

| A.2  | Handel-C/ANSI-C comparison iii                                       |

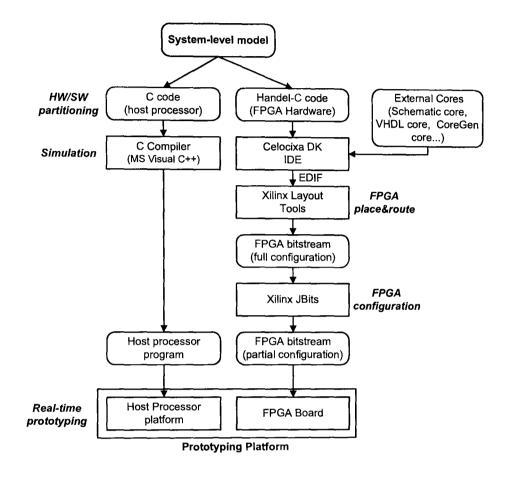

| A.3  | Handel-C design flow iv                                              |

| A.4  | The PAR construct vi                                                 |

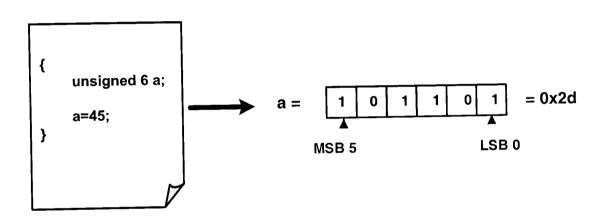

| A.5  | Variables declaration example vi                                     |

| A.6  | Bit level operators in Handel-C vii                                  |

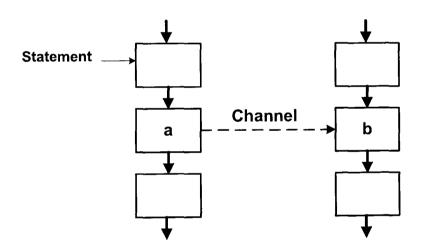

| A.7  | Channel communication vii                                            |

| A.8  | RAM/ROM declaration in Handel-C viii                                 |

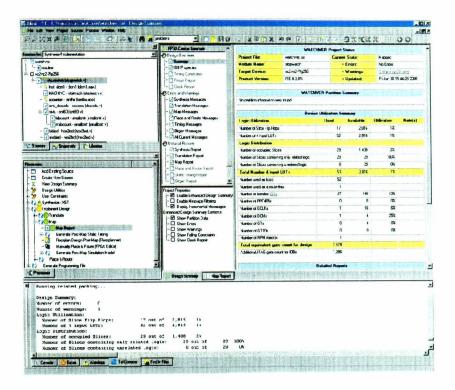

| A.9  | Sample window displaying ISE Project Navigator                       |

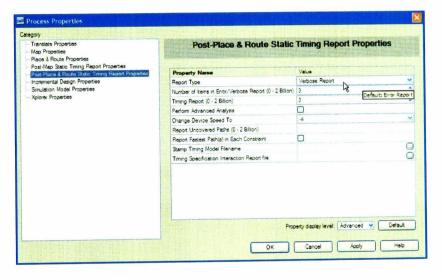

| A.10 | Setting the design options in ISE                                    |

| A.1  | 1 Setting constraints in the timing editor                           |

| A.1  | 2 PACE xi                                                            |

| A.13 | FPGA Editor showing a section of the clock tree in a design xiii          |

|------|---------------------------------------------------------------------------|

| A.14 | XPower xiv                                                                |

| A.15 | NLREG                                                                     |

| B.1  | RC1000 functional block diagram xvii                                      |

| B.2  | Host-FPGA communication                                                   |

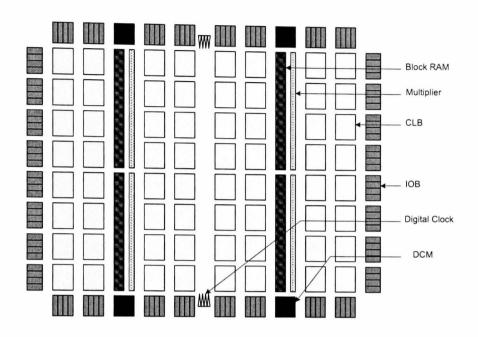

| B.3  | Virtex-E architecture overview                                            |

| B.4  | Virtex-E local routing                                                    |

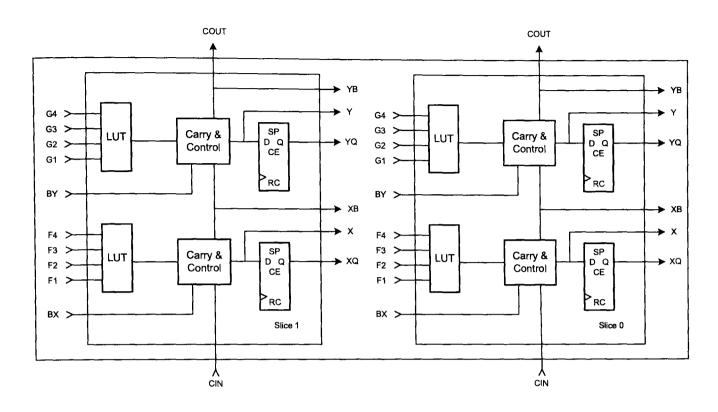

| B.5  | 2-Slice Virtex-E CLB                                                      |

| B.6  | Virtex-II platform FPGA                                                   |

| B.7  | Virtex-II Pro FPGA platform                                               |

| B.8  | Spartan-3L Pro FPGA platform                                              |

| B.9  | Virtex-4 complete feature set with the chip in background xxvi            |

| C.1  | FRAT basis function (projection kernel) for blocksize $p = 7$ and $k =$   |

|      | 4. The digital line superimposed over the kernel corresponds to $l=4$ xxx |

| C.2  | Finite Ridgelet transform obtained by performing DWT on the FRAT          |

|      | vectors                                                                   |

| C.3  | RGB to YCrCb conversion                                                   |

# List of Tables

| 3.1 | Implementation results                                             |

|-----|--------------------------------------------------------------------|

| 3.2 | Power dissipation data                                             |

| 3.3 | On-chip dynamic power at constant frequency 80                     |

| 3.4 | Comparison of design metrics with existing architectures 88        |

| 3.5 | Implementation results for different FPGA platforms 90             |

| 3.6 | Comparison of implementation results for the Virtex-E platform 90  |

| 3.7 | $EOP$ metrics obtained for $N = 4, 8, 16 \dots 92$                 |

| 3.8 | $EA$ values obtained for $N = 4, 8, 16 \dots 93$                   |

| 3.9 | Implementation results                                             |

| 4.1 | Comparison with existing architectures                             |

| 4.2 | PSNR of images reconstructed from 8 BPP Radon domain standard      |

|     | images                                                             |

| 4.3 | Performance metrics for the Virtex-E platform                      |

| 4.4 | FPGA implementation - comparison of area (number of slices) with   |

|     | existing architectures                                             |

| 4.5 | Comparison of performance with existing architectures for the case |

|     | p=7                                                                |

| 4.6 | EPP (nJ) for the proposed parallel FRAT core on the Virtex-E FPGA  |

|     | platform                                                           |

| 4.7 | Entropy measures for Source, FRAT, Wavelet and FRIT domain im-     |

|     | ages using different wavelet filters                               |

| 4.8 | Comparison of design parameters of the Radon block with existing   |

|     | architectures                                                      |

| 4.9  | Performance metrics for the FRIT IP Core on the FPGA and ASIC                             |

|------|-------------------------------------------------------------------------------------------|

|      | platforms. Maximum frequency is in MHz and throughput is denoted                          |

|      | in Million pel/sec                                                                        |

| 4.10 | Comparison of performance metrics with existing architectures in place 126                |

| 4.11 | Key FPGA performance metrics of the proposed DA-Based FIR Filter                          |

|      | (for Word-Length $L=8$ )                                                                  |

| 4.12 | Comparison of performance of the proposed architecture with existing                      |

|      | work                                                                                      |

| 4.13 | Power dissipation of the proposed FPGA implementation of FIR filter                       |

|      | for different filter orders and address-lengths                                           |

| 4.14 | Content of the ROM $i$ $(0 \le i \le 2)$                                                  |

| 4.15 | Performance comparison with existing CSC cores                                            |

| 5.1  | Area (slice) metrics under various levels of parallelism                                  |

| 6.1  | Final estimates of the scaling coefficients                                               |

| 6.2  | Coefficient values for the area and power models (Virtex-E Platform) 179                  |

| 6.3  | Coefficient values for area and power models for the proposed FRAT                        |

|      |                                                                                           |

|      | reference architecture                                                                    |

| 6.4  | reference architecture                                                                    |

| 6.4  |                                                                                           |

| 6.4  | Coefficient values for area and power models for the proposed FRAT                        |

|      | Coefficient values for area and power models for the proposed FRAT parallel architecture  |

|      | Coefficient values for area and power models for the proposed FRAT  parallel architecture |

| 6.5  | Coefficient values for area and power models for the proposed FRAT  parallel architecture |

| 6.5  | Coefficient values for area and power models for the proposed FRAT  parallel architecture |

| 6.5  | Coefficient values for area and power models for the proposed FRAT  parallel architecture |

| 6.5  | Coefficient values for area and power models for the proposed FRAT  parallel architecture |

### List of Abbreviations

**3G**: Third Generation

**4G**: Fourth Generation

AC: Area Complexity

AG: Address Generator

ALI: Address Logic Initialiser

**ASIC:** Application Specific Integrated Circuit

**BPP**: Bits Per Pixel

CAD: Computer Aided Design

**CAFD**: Cycle Accurate Functional Description

CDFG: Control-Data Flow Graph

CDMA: Code Division Multiple Access

**CLB**: Configurable Logic Block

CMOS: Complementary Metal Oxide Semiconductor

**CORDIC:** COordinate Rotation DIgital Computer

**CP**: Clock Power

CPLD: Complex Programmable Logic Device

CSC: Colour Space Conversion

**DA**: Distributed Arithmetic

**DBWT**: Discrete Bi-orthogonal Wavelet Transform

**DCT**: Discrete Cosine Transform

**DFF**: D Flip Flop

**DFG**: Data Flow Graph

**DFT**: Discrete Fourier Transform

**DHT**: Discrete Hartley Transform

**DMT**: Discrete Multi-Tone

**DOT**: Discrete Orthogonal Transform

**DP**: Dynamic Power

**DSL**: Digital Subscriber Line

**DSP**: Digital Signal Processing/Processor

**DVS**: Dynamic Voltage Scaling

EDIF: Electronic Design Interchange Format

**EN**: Electronic Nose

FDS: Force Directed Scheduling

**FFT:** Fast Fourier Transform

FHT: Fast Hadamard Transform

FIR: Finite Impulse Response

FLPAM: Functional Level Power Analysis and Modelling

FMAT: FPGA MATrix Algorithms

FPGA: Field Programmable Gate Array

FRAT: Finite Radon Transform

FRIT: Finite Ridgelet Transform

GMM: Gaussian Mixture Modelling

**GPP**: General Purpose Processor

HDL: Hardware Definition Language

**HDTV**: High Definition TeleVision

HKUST: Hong Kong University of Science and Technology

HT: Hadamard Transform

I/O: Input/Output

IC: Integrated Circuit

InP: Inner Product

**IP**: Intellectual Property

IpP: Input Power

JHDL: Just-Another Hardware Description Language

KLT: Karhunen Loeve Transform

KNN: K-Nearest Neighbour

LE: Logic Element

LFSR: Linear Feedback Shift Registers

LP: Logic Power

LPW: Linear PieceWise

LSB: Least Significant Bit

LUT: Look Up Table

MB: Memory Block

MIMO: Multi Input Multi Output

MLP: Multi-Layer Perceptron

MRI: Magnetic Resonance Imaging

MSB: Most Significant Bit

NRE: Non Recurring Expenditure

NTT: Number Theoretic Transform

NTU: Nanyang Technological University

**OBC**: Offset Binary Coding

**OFDM**: Orthogonal Frequency-Division Multiplexing

**OP**: Output Power

PACE: Pinout Area Constraints Editor

PAL: Programmable Array Logic

PAR: Place and Route

PDA: Personal Digital Assistant

PE: Processing Element

PLD: Programmable Logic Device

PPCA: Probabilistic Principal Component Analysis

PRCCV: Parallel and Reconfigurable Computing for Computer Vision

PSNR: Peak Signal to Noise Ratio

$\mathbf{R} \& \mathbf{D}$ : Research and Development

RAM: Random Access Memory

RBF: Radial Basis Functions

**ROM**: Read Only Memory

RT: Radon Transform

RTL: Register Transfer Level

S2IS: Smart Sensory Integrated Systems

SA: Shift Add

SDR: Software Defined Radio

SF: Self Force

SIPOSR: Serial-In Parallel-Out Shift Register

SoC: System on Chip

SoPC: System on a Programmable Chip

SP: Signal Power

SRAM: Static Random Access Memory

StP: Static Power

SVD: Singular Value Decomposition

TC: Time Complexity

TDM: Time Division Multiplexing

**VPR**: Versatile Place and Route

WCDMA: Wideband Code Division Multiple Access

W-H: Walsh-Hadamard

WHT: Walsh-Hadamard Transform

WiFi: Wireless Fidelity

$\mathbf{WiMAX}: \ \ \mathbf{Worldwide} \ \mathbf{Interoperability} \ \mathbf{for} \ \mathbf{Microwave} \ \mathbf{Access}$

WTA: Winner Take All

$\mathbf{XCL}$ : Xilinx Coregen Library

### Chapter 1

### Introduction

Digital image and signal processing is one of the fastest growing areas of the electronics industry. These technologies are having an increasing impact in a wide variety of application areas such, wireless communications, biometrics, biomedical imaging, multimedia indexing storage & retrieval, computer vision and remote sensing.

State-of-the-art signal processing has changed the way we characterise and solve many applications, especially those involving increasingly sophisticated algorithms that require real-time processing of high volumes of data. Increasing demands for faster and more sophisticated processing show absolutely no sign of abating for signal processing applications.

In the context of Digital Signal Processing (DSP), the wired and wireless communications markets are exploding with a multiplicity of hi-demand standards such as Wireless Fidelity (WiFi), Worldwide Interoperability for Microwave Access (WiMAX), Third Generation (3G), Fourth Generation (4G) and Wideband Code Division Multiple Access (WCDMA) system standards, application standards such as Orthogonal Frequency-Division Multiplexing (OFDM) and Multi Input Multi Output (MIMO), as well as technology standards such as Software Defined Radio (SDR). In other areas such as classification, a number of complex algorithms including non-linear functions, statistical techniques such as mixture modelling, intelligent approaches such as neural-networks are scaling up computational complexity towards newer records.

Additionally, a continuous stream of changes is also erupting from the audio, video

and broadcast markets as well as the defense electronics industry. Within the context of image processing, emerging ultra-high complexity application areas include face recognition, 3D medical volume segmentation, new generation and higher dimensional transforms for image representation and consumer driven technologies such as High Definition TeleVision (HDTV).

The following key examples richly illustrates the challenges signal processing system developers must be prepared to address. In a Discrete Multi-Tone (DMT) modulation based Digital Subscriber Line (DSL) transceiver, it is necessary to compute transform of order as high as 4096 at sampling rate up to 44.16 MHz [1]. Similarly, in a video processor it is necessary to compute O(10) of 8-point transform samples for encoding/decoding of a single image of  $(512 \times 512)$  pixels. Moreover, the computational demand has been increasing with time along with the widespread use of multimedia communication.

Application designers face many new and difficult challenges as they attempt to deploy technology that can execute high-performance computations, manipulate larger and larger data sets and better visualise increasingly complex data. These needs must be balanced with the constraints of rising costs, shrinking space, legacy systems, mobility and power constraints and a lack of sufficient human resources. To help address these needs, appropriate choices need to be made at every stage of the design process.

Hardware acceleration has become inevitable for providing the necessary performance that is demanded for image and signal processing applications. Hardware design paradigms are also undergoing a sea change in order to address the various issues involved. There is a perceptible shift towards top-down design flow and a preference for modular, integrated and flexible solutions.

#### 1.1 Hardware Acceleration

A lot of research has been carried out into several areas of architectural support for complex applications using DSPs and special purpose hardware [2]. Conventional approaches for hardware acceleration are listed below.

#### 1.1.1 Digital Signal Processors

One method of increasing the performance of a General Purpose Processor (GPP) is to attach a specialised processing unit in the form of DSP. DSP processors have features designed to support high-performance, repetitive and numerically intensive tasks. Features that accelerate performance in DSP applications include:

- Single-cycle multiply-accumulate capability. High-performance DSPs often have two multipliers that enable two multiply-accumulate operations per instruction cycle;

- Most DSPs provide various configurations of on-chip memory and peripherals tailored for DSP applications. DSPs generally feature multiple-access memory architectures that enable DSPs to complete several accesses to memory in a single instruction cycle;

- Specialised execution control. Usually, DSP processors provide a loop instruction that allows tight loops to be repeated without spending any instruction cycles for updating and testing the loop counter or for jumping back to the top of the loop; and

- DSP processors are known for their irregular instruction sets, which generally allow several operations to be encoded in a single instruction. For example, a processor that uses 32-bit instructions may encode two additions, two multiplications and four 16-bit data moves into a single instruction. In general, DSP processor instruction sets allow a data move to be performed in parallel with an arithmetic operation. GPPs, in contrast, usually specify a single operation per instruction.

As a result, DSPs have been successfully used in a wide range of image processing applications [3,4]. They provide the computing power necessary to process large amounts of data in real-time [5].

# 1.1.2 Special Purpose Application Specific Integrated Circuits Hardware

The other method which gives better performance for particular applications is the use of Application Specific Integrated Circuits (ASICs). They are designed specifically to perform a given computation and consequently they efficiently perform the given computation according to the application's design objectives which may be to optimise for one or more of design flexibility, performance, power consumption and area. However, after fabrication the circuit can not be altered. This forces a redesign and a re-fabrication of any part of the chip which requires modification. This is an expensive process, especially when one consider the difficulties in replacing ASICs in a large deployed system [2,6].

The main disadvantages of this approach can be summarised in the three following points:

- Special purpose hardware has a long development time, from design through simulation and fabrication;

- It can also be expensive if it is a one-off solution or if the volume required cannot justify its fabrication costs; and

- Once this special purpose hardware is built, it is not possible to change the hardware to accommodate slightly different needs. With such a solution a new piece of hardware is usually required for each new algorithm.

A new breed of ASIC products, called "Structured ASIC", can cut Non-Recurring Expenditure (NRE) expenses by more than 90% for derivative chips and speedup time-to-market. The underlying concept behind structured ASICs is actually fairly simple. Although there are a wide variety of alternative architectures, they are all based on a fundamental element called a "tile" by some or a "module" by others. This tile contains a small amount of generic logic implemented either as gates and/or multiplexers and/or a Look-Up Table (LUT). Depending on the particular architecture, the tile may contain one or more registers and possibly a very small amount of local Random Access Memory (RAM). An array (sea) of these tiles is then

prefabricated across the face of the chip. Structured ASICs also typically contain additional prefabricated elements, which may include configurable general-purpose Input/Output (I/O), microprocessor cores, gigabit transceivers, embedded (block) RAM and so forth. When compared with standard cell-based ASICs, structured ASICs offer shorter turnaround time and require less NRE charges for future functional changes. Structured ASIC technology is especially suitable for platform ASIC designs that have integrated most of the Intellectual Property (IP) blocks and leave some space for custom changes [7,8].

A more recent approach, which aims to benefit from the advantages of special purpose hardware by avoiding many of its disadvantages, is to use dynamically reprogrammable hardware in the form of Field Programmable Gate Arrays (FPGAs). An overview of this technology is provided in the next section.

#### 1.2 Field Programmable Gate Arrays: A Review

Since their introduction in 1985, FPGAs have steadily established themselves as an alternative for implementing digital logic in systems. First generation FPGAs were used to provide a denser solution for glue logic, but now they have expanded their applications to the point that it is not uncommon to find FPGAs as the central processing devices within systems.

The early FPGA devices from Xilinx, Altera and others provided relatively little logic, but later generations provided enough logic for researchers to consider FPGAs for direct implementation of computational algorithms in reconfigurable logic devices. The densities of todays FPGAs have exceeded 150,000 4-input LUTs per device and some have developed into devices that can be used to build complete Systems On a Programmable Chip (SoPC), providing such specialised features as DSP blocks, multi-gigabit serial I/O, embedded microprocessors and embedded Static RAM (SRAM) blocks of various sizes.

### 1.2.1 FPGA Structure

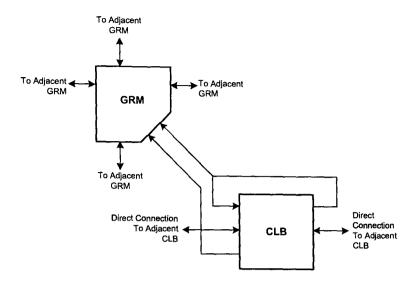

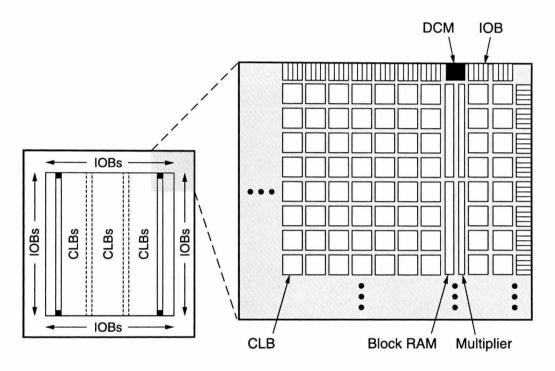

The basic architecture of FPGAs consists of three kinds of components: logic blocks, routing and I/O blocks. Generally, FPGAs consist of an array of programmable logic blocks that can be interconnected to each other as well as to the programmable I/O blocks through some sort of programmable routing architecture. Figure 1.1 provides a very simplified diagram of a generic FPGA architecture.

Figure 1.1: Generic FPGA structure showing internal blocks

### A Basic Logic Block

As shown in Fig. 1.1, a typical FPGA has a logic block with one or more 4-input LUT, optional D Flip-Flops (DFF) and some form of fast carry logic. The LUTs allow any function to be implemented, providing generic logic. The DFF can be used for pipelining, registers, state holding functions for finite state machines, or any other situation where clocking is required. The fast carry logic is a special resource provided in the cell to speed up carry-based computations, such as addition, parity, wide logical AND operations and other functions.

### Routing

Most FPGA architectures organise their routing structures as a relatively smooth sea of routing resources, allowing fast and efficient communication along the rows and columns of logic blocks. The logic blocks are embedded in a general routing structure, with input and output signals attaching to the routing fabric through connection blocks as shown in Fig. 1.1 [9].

#### Connection Blocks

The connection blocks provide programmable multiplexers, selecting which of the signals in the given routing channel will be connected to the logic block's terminals. These blocks also connect shorter local wires to longer distance routing resources. Signals flow from the logic block into the connection block and then along longer wires within the routing channels [9].

#### **Switch Boxes**

At the switch boxes there are connections between the horizontal and vertical routing resources to allow signals to change their routing direction. Once the signal has traversed through routing resources and intervening switch boxes, it arrives at the destination logic block through one of its local connection blocks. In this manner, relatively arbitrary interconnections can be achieved between the logic blocks in the system. While the routing architecture of an FPGA is typically quite complex - the connection blocks and switch boxes surrounding a single logic block typically have thousands of programming points - they are designed to be able to support fairly arbitrary interconnection patterns [9].

Detailed descriptions of the FPGA devices that have been used in this research are presented in Appendix B.

### 1.2.2 FPGA Design Entry and Synthesis

A typical design flow for FPGA design is given in Figure 1.2. It consists of a number of tools: high-level design languages, Hardware Description Languages (HDLs),

Figure 1.2: FPGA design cycle

schematic capture tools, netlist converters and Place And Route (PAR) tools. Handel-C has been used for most implementations carried out in this research project. Full details about the various tools used to synthesise the designs presented in this research work are presented in Appendix A.

# 1.3 Opportunities in Deploying FPGA Based Solutions

# 1.3.1 The Importance of FPGAs in Digital Logic Implementation

Reconfigurable hardware in the form of FPGAs is an extremely powerful implementation approach for several reasons. First and foremost, it allows for truly parallel

computations to take place in a circuit. Many modern GPPs and operating systems can emulate parallelism by switching tasks very rapidly. Having operations occur in a parallel fashion results in a much faster overall processing time. This is the case even though the clock speed of the FPGA is lower than that of the GPPs. Prototyping is also a compelling reason to use FPGAs in the initial design phase. The description of a system can be written and actual hardware can be created to test instead of simply relying on simulators or dead reckoning inside of design. This allows a design to be thoroughly tested and debugged before an ASIC is created, saving on production costs. FPGAs are everywhere. Companies use them on development boards to help refine new chip designs. Students use them in the classroom to run experiments. Companies and universities are using them in cutting-edge research on topics ranging from programming technology, cryptography to real-time systems. As a result of rapid advances in the semiconductor industry, FPGAs themselves are getting so inexpensive that some companies do not even fabricate an ASIC. They simply include the FPGA in their final product. The considerable interest in reconfigurable hardware has been highlighted by an increasing amount of research carried out in the area, coupled with the development of several commercial systems based on FPGAs. There is no doubt that this level of interest will certainly continue to grow over the next number of years. With the emergence of such reconfigurable hardware it is not surprising that there has been wide ranging research into the use of FPGAs to increase the performance of a wide range of computationally intensive applications.

With soft cores, dedicated logic, block multipliers and specialised versions available in modern FPGAs, they are being increasingly deployed in computationally intensive application areas involving image and signal processing. The regular nature of the complex computations performed repeatedly within such application areas are well suited to a hardware based implementation using FPGAs.

### 1.3.2 In Field Design Upgradation and Future Proofing

Future proofing in FPGA based designs is a function of two different issues:

• Field FPGA reconfiguration, driven by bug fixes, changing standards, equip-

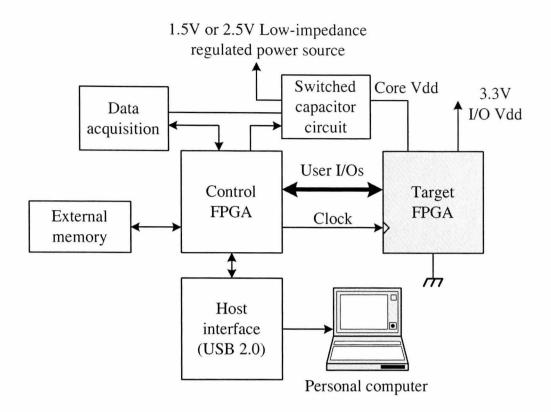

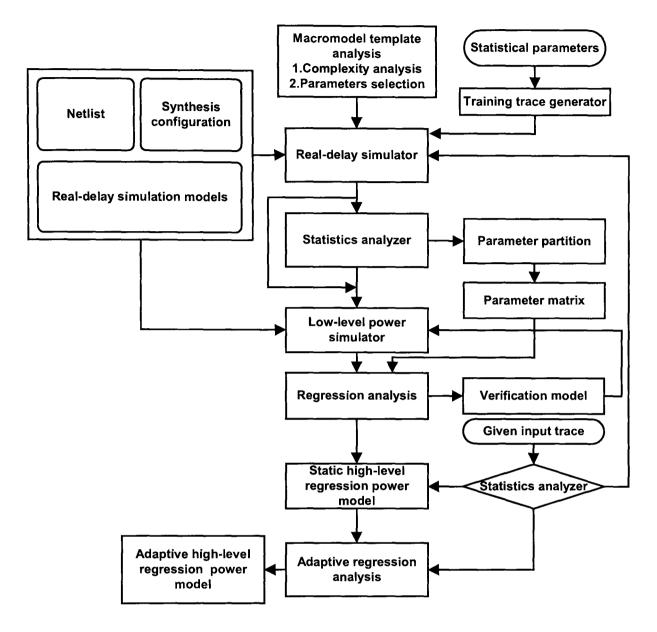

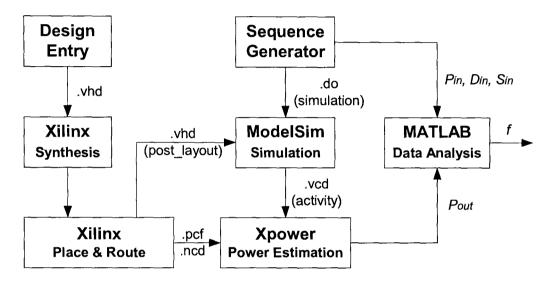

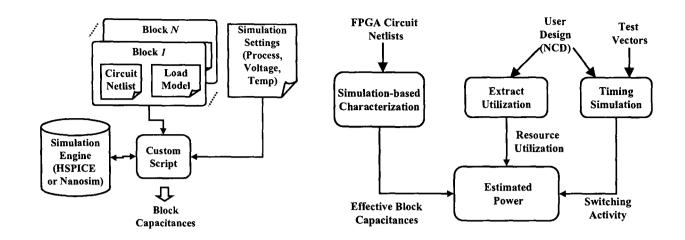

ment upgrades and addition of services, continues to grow rapidly in importance.