# EMSN: An Energy-Efficient Memristive Sequencer Network for Human Emotion Classification in Mental Health Monitoring

Xiaoyue Ji, Student Member, IEEE, Zhekang Dong, Senior Member, IEEE, IEEE, Yifeng Han, Chun Sing Lai, Senior Member, IEEE, Guangdong Zhou, Donglian Qi, Senior Member, IEEE

Abstract—Mental health problems are an increasingly common social issue severely affecting health and well-being. Multimedia processing technologies via facial expression show appealing prospects in the consumer field for mental health monitoring, while still suffer from intensive computation and low energy efficiency. This paper proposes an energy-efficiency memristive sequencer network (EMSN) for human emotion classification, which offers an environmentally friendly approach for consumers with low cost and easily deployable hardware. Firstly, twodimensional (2D) materials are employed to construct an ecofriendly memristor, the efficacy and reliability of which are confirmed through performance testing. Then, a sequencer block is proposed using memristive circuits. Notably, it is a core component of the EMSN, consisting of a bidirectional long shortterm memory circuit, normalisation circuit module, and multilayer perception module. After combining some necessary function modules, the EMSN can be achieved. Furthermore, the proposed EMSN is applied for human emotion classification. The experimental results demonstrate that the proposed EMSN has advantages in computational efficiency and classification accuracy compared to existing mainstream methods, indicating an advancement in consumer health monitoring.

Index Terms—Human emotion classification, memristive circuit, two-dimensional (2D) materials, sequencer network.

#### I. INTRODUCTION

uman emotion and feeling are fundamental to human experience, health and well-being, influencing cognition, memory, and targeted activity behavior such as learning, communication, and rational decision-making [1]. Mental health problems caused by negative emotions usually lead to diseases such as depression, addiction, and heart attack, which may severely affect quality of life [2]. Mental health monitoring is particularly urgent and important, especially for the development of sound mind and body. Considering facial expression is one of the most natural and universal signals for consumers to convey their emotional states and behavior intentions, multimedia processing technology

using facial expression plays a vital role to understand and analyse mental states in consumer health monitoring [3]. Advanced research on artificial intelligence and psychology technology, numerous artificial neural networks, such as multilayer neural networks (MNNs) [4], convolutional neural networks (CNNs) [5-7], long short-term memory (LSTM) networks [8-10], and transformer networks [11], have been conducted on automatic human emotion classification to establish the relationship between facial expression and consumer mental health. Nevertheless, such multimedia processing approaches rely on conventional Von Neumann architecture, which requires physical separation of the processor and the memory. Meanwhile, this computing architecture fails to adequately accommodate the efficient parallel computation, active data access, and low-power consumption.

Neuromorphic computing is inspired by the functioning of the brain [12]. It has been used to establish an abiotic computing system in which the functioning resembles the human brain and to create ultra-low-power computers that possess autonomous learning and cognitive capabilities. Hence, this strategy makes it possible to achieve circuit implementation of different multimedia processing systems. So far, a number of neuromorphic computing systems have been proposed using different consumer electronics devices, such as spintronic devices, ferroelectric devices, and complementary phasechange memory devices [13]. Memristors are two-terminal electronic devices that exhibit non-volatility, high density, long retention, and long endurance and are potential candidates for neuromorphic computing [14]. Memristor was developed by Leon O. Chua in 1971 [15]. It is the fourth basic circuit element and is also linked to the physical devices introduced in 2008 by R. Stanley Williams and his team at Hewlett-Packard Labs [16]. With the development of memristor technology, this neuromorphic computing device has been proved effective in

Manuscript received November 02, 2022.

This work was supported in part by the National Natural Science Foundation of China under Grant 62001149, Natural Science Foundation of Zhejiang Province under Grant LQ21F010009, and Fundamental Research Funds for the Provincial University of Zhejiang under Grant GK229909299001-06. (Corresponding authors: Zhekang Dong and Chun Sing Lai).

X. Ji and Y. Han are with the College of Electrical Engineering, Zhejiang University, Hangzhou 310027, China (e-mail: <u>ji.xiaoyue@zju.edu.cn</u>; <u>hanyf@zju.edu.cn</u>).

- Z. Dong is with the School of Electronics and Information, Hangzhou Dianzi University, Hangzhou 310018, China (e-mail: englishp@126.com).

- C. S. Lai is with the Department of Electronic and Computer Engineering, Brunel University London, London, UB8 3PH, UK and also with the School of Automation, Guangdong University of Technology, Guangzhou, China 510006 (email: <a href="mailto:chunsing.lai@brunel.ac.uk">chunsing.lai@brunel.ac.uk</a>).

- G. Zhou is with the College of Artificial Intelligence, Southwest University, Chongqing 400715, China (e-mail: <a href="mailto:zhougd@swu.edu.cn">zhougd@swu.edu.cn</a>).

- D. Qi is with the Hainan Institute of Zhejiang University, Sanya 572025, China (e-mail: qidl@zju.edu.cn).

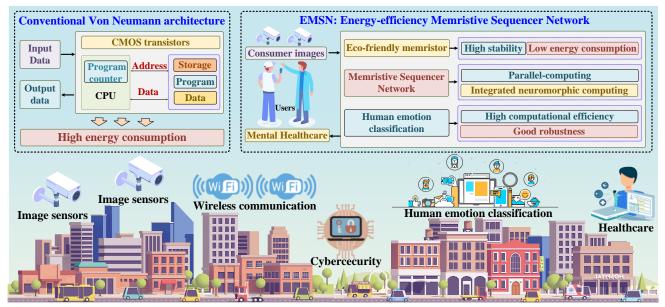

Fig. 1. Systemic comparison of von Neumann based multimedia processing systems and the proposed EMSN

the fields of artificial intelligent and computer vision [17-19]. A fully hardware-based memristive multilayer neural network demonstrated a recognition accuracy of 93.63% on a handwritten digit dataset [17]. The full-circuit implementation of the transformer network in accordance with the memristor was proposed, it can be used to realize character recognition [18]. A multimodal neuromorphic sensory-processing system for smart home applications was proposed in [19], offering an environmentally friendly method with easily deployable hardware. However, the current neuromorphic computing systems still suffer from some limitations. At the device level, the device variations may cause inaccurate encoding of network weights in neuromorphic computing because of immature fabrication technology and unstable material performance. Therefore, the neuromorphic computing devices with high stability are required. At the system level, efforts are needed to develop high performance processing algorithms that can realize a high-accuracy, consumer-friendly, and energyefficient neuromorphic computing system.

Sequencer networks [20], one of the most important models for computer vision, have achieved state-of-the-art recognition accuracy and exceeded previous results in image classification. Despite the merits of sequencer network, the corresponding hardware implementation of sequencer network has not been developed due to the complex calculation process and data storage. In this work, we propose an energy-efficiency memristive sequencer network (EMSN), aiming at solving von Neumann bottleneck (mainly refer to high energy consumption) emerging in consumer health monitoring. The systemic comparison of von Neumann based multimedia processing systems and the proposed EMSN is provided in **Fig. 1**. The main contributions of this work are summarised below:

- 1) An Ag-Au/M<sub>o</sub>Se<sub>2</sub>-doped Se/Au-Ag memristor with high stability is prepared. It is a promising candidate to emulate high-accuracy neuromorphic computing for consumer health monitoring.

- 2) The circuit design of EMSN is proposed, which avoids the

separation of weight representation and computing, enabling a parallel-computed and highly integrated neuromorphic computing.

3) The correctness of the proposed EMSN is verified by human emotion classification. The results show that the proposed EMSN outperforms the existing state-of-the-art methods with high computational efficiency and good robustness.

The rest of this paper is structured as follows. Section II describes the fabrication and performance testing of the Ag-Au/ $M_0Se_2$ -doped Se/Au-Ag memristor. Section III demonstrates the overall architecture and the circuit-level design. In Section IV, the proposed system is applied to human emotion classification for verification. Finally, Section V presents the conclusion and future direction of the study.

## II. MEMRISTOR FABRICATION AND PERFORMANCE TESTING

## A. Fabrication of Ag-Au/MoSe<sub>2</sub>-doped Se/Au-Ag Memristor

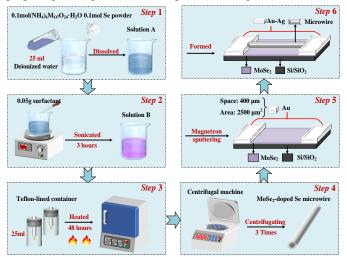

The fabrication of the Ag-Au/M<sub>O</sub>Se<sub>2</sub>-doped Se/Au-Ag memristor relies on the hydrothermal synthesis and the magnetron sputtering methods [21]. Specifically, the hydrothermal synthesis method is adopted to fabricate MoSe<sub>2</sub>-doped Se microwires, and the magnetron sputtering method is used to prepare the Ag-Au electrodes (as shown in **Fig. 2**).

- **Step 1**: Solution A is prepared by dissolving 0.1 moL Se powder and 0.1 moL ammonium molybdate (NH<sub>4</sub>)<sub>6</sub>M<sub>O7</sub>O<sub>24</sub>·H<sub>2</sub>O into 25 mL deionised water.

- **Step 2**: Solution B is prepared through the addition of 0.05 g surfactant (hexadecyl trimethyl ammonium bromide) to Solution A, after which it is continuously sonicated for 3 hours with the assistance of a magnetic stirrer.

- **Step 3**: Solution B is placed in a 25 mL Teflon-lined container, after which it is heated in a muffle furnace for 48 hours at 227°C.

- **Step 4**: Following 3 times centrifugation, the MoSe<sub>2</sub>-doped Se microwire is secured from the heated Solution B.

**Step 5**: The magnetron sputtering technique is employed to generate the Au electrode (space =  $400 \mu m$ , area =  $2,500 \mu m^2$ ) on the Si/SiO<sub>2</sub> substrate.

**Step 6**: A four-probe test is used to select the MoSe<sub>2</sub>-doped Se microwire, after which the microwire ends are fixed in the Au electrode and coated with a layer of Ag adhesive, thereby preparing the Ag-Au/MoSe<sub>2</sub>-doped Se/Au-Ag memristor.

**Fig. 2.** The fabrication flow of Ag-Au/MoSe<sub>2</sub>-doped Se/Au-Ag memristor

## B. Performance Testing

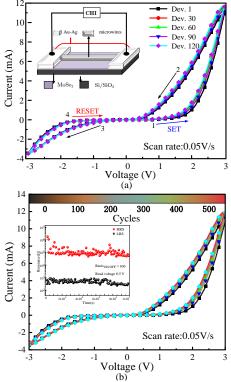

The performance testing of Ag-Au/MoSe<sub>2</sub>-doped Se/Au-Ag memristor is carried out through an electrochemical workstation (CHI-600D). The electrical characteristics are measured with  $\pm 3$  V scanning voltages with a scan rate of 0.05 V/s, as shown in **Fig. 3**.

**Fig. 3.** The performance testing of Ag-Au/ M<sub>o</sub>Se<sub>2</sub>-doped Se/Au-Ag (a) device-to-device analysis; (b) cycle-to-cycle analysis

The measured I–V curves acquired by 120 memristors are indicative of extensive overlap. In addition, the inset comprises a structural depiction of the fabricated memristor. The findings from the testing indicate that Ag-Au/MoSe<sub>2</sub>-doped Se/Au-Ag memristors possess robust device-to-device steadiness, as demonstrated in Fig. 3(a). The overall I-V curves are asymmetrical in the positive and negative voltage regions, indicating that the fabricated memristors exhibit electronic resistive switching memory behavior. Specifically, in the first stage, the memristors remain in the high-resistance state (HRS). The scanning voltages rise from 0 V to 3 V. For this reason, the device currents are virtually unaltered up to the point that the scanning voltages surpass 1.5 V, after which the device currents begin rising up to the maximum 3 V. This indicates that the "SET" process is finished. The memristors continue to demonstrate a low-resistance state (LRS) in the second and third stages, when the scanning voltages decrease from 3 V to -3 V. In the fourth stage, the current progressively declines in accordance with changes in the scanning voltage from -3 V to 0 V. The memristor alters from LRS to HRS when the scanning voltage exceeds -1.5 V, thereby indicating completion of the "RESET" process.

The stability of the memristor can be examined by measuring the I–V curves for the 1<sup>st</sup>, 10<sup>th</sup>, 50<sup>th</sup>, 200<sup>th</sup>, and 500<sup>th</sup> cycles, whereby the inset comprises the resistance variation curve under 0.5 V reading voltage for 10<sup>5</sup> seconds (**Fig. 3(b)**). It can be maintained the extensive overlap in the I–V curves and the resistance ratio that is present between the HRS and LRS, indicating that the fabricated memristor is sufficiently stable.

#### III. CIRCUIT DESIGN OF MEMRISTIVE SEQUENCER NETWORK

## A. The Architecture of Sequencer Network

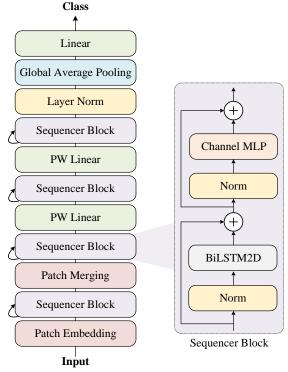

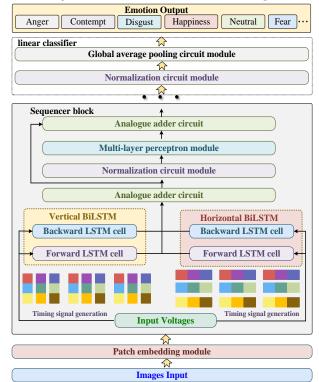

According to [22], Visual Transformer (ViT) and its variants based on a self-attention module have proved effective in many computers vision tasks. Several works have tried to replace the self-attention module with other modules (e.g., the global filter) [23]. Following this trend, the sequencer network replaces the self-attention layer with bidirectional long short-term memory (BiLSTM). The specific structure of the sequencer network can be seen in **Fig. 4**.

The sequencer network can be divided into two parts: the sequencer block and the other necessary function modules (e.g., the layer normalisation module). Notably, the sequencer block is the basic component of the sequencer network and consists of two parts: a BiLSTM2D layer and a multi-layer perceptron.

The BiLSTM2D layer consists of a vertical BiLSTM layer and a horizontal BiLSTM layer, which can effectively be spatial and global information to memory. The mathematical expression of BiLSTM2D is given by:

$$\begin{cases}

H_{vertical} = \text{BiLSTM}(X_w) \\

H_{horizontal} = \text{BiLSTM}(X_h)

\end{cases}$$

(1)

$$BiLSTM\ 2D = concatenate(H_{vertical}, H_{horizontal})$$

(2)

where  $X_w$  and  $X_h \in R^{H \times W \times C}$  are the input to the vertical BiLSTM layer and the horizontal BiLSTM layer, respectively; H and W denote the number of sequences in the vertical and horizontal directions, respectively; C represents the channel dimension;  $H_{vertical}$  and  $H_{horizontal} \in R^{H \times W \times 2D}$  are the output of the vertical

BiLSTM layer and the horizontal BiLSTM layer, respectively; D = C/4 is the hidden dimension. BiLSTM(·) refers to the BiLSTM layer. It consists of two parallel LSTM layers: one takes the input in a forward direction (LSTM<sub>forward</sub>), while the other takes it in a backward direction (LSTM<sub>backward</sub>).

Fig. 4. The structure of sequencer network

Specifically, we assume  $\vec{x}$  to be the input series, and  $\vec{x}$  is the rearrangement of  $\vec{x}$  in reverse order. Then, the outputs of these two LSTM layers can be written by:

$$\begin{cases} \vec{h}_{forward} = \text{LSTM}_{forward} (\vec{x}) \\ \vec{h}_{backward} = \text{LSTM}_{backward} (\bar{x}) \end{cases}$$

(3)

$$BiLSTM = concatenate(\vec{h}_{forward}, \vec{h}_{backward})$$

(4)

where LSTM( $\cdot$ ) denoting the LSTM layer can be mathematically expressed by:

$$i_{t} = \sigma(W_{x,i}x_{t} + W_{h,i}h_{t-1} + b_{i})$$

$$f_{t} = \sigma(W_{x,f}x_{t} + W_{h,f}h_{t-1} + b_{f})$$

$$c_{t} = f_{t} \odot c_{t-1} + i_{t} \odot \tanh(W_{x,c}x_{t} + W_{h,c}h_{t-1} + b_{c})$$

$$o_{t} = \sigma(W_{x,o}x_{t} + W_{h,o}h_{t-1} + b_{o})$$

$$h_{t} = o_{t} \odot \tanh(c_{t})$$

(5)

where  $i_t$  denotes the input gate that controls the storage of input  $x_t$ ;  $f_t$  denotes the forget gate that controls the previous cell state  $c_{t-1}$ ;  $o_t$  denotes the output gate that controls the cell output  $h_t$  from the current cell state  $c_t$ ;  $\sigma$  and  $\Theta$  are the logistic sigmoid and Hadamard product, respectively; weight matrixes  $W(W_{x,i}, W_{x,f}, W_{x,c}, W_{x,o}, W_{h,i}, W_{h,f}, W_{h,c}, W_{h,o})$  are learnable parameters; and  $b(b_i, b_f, b_c, b_o)$  is the bias of LSTM.

The multi-layer perceptron consists of two-layer linear transformations with a ReLU activation function in between, it can be written by:

$$MLP(L_{o1}) = \max(L_{o1}W_1 + b_1)W_2 + b_2$$

(6)

where  $MLP(\cdot)$  denotes the multi-layer perceptron operation;  $L_{01}$  is the input of the multi-layer perceptron; weight matrixes ( $W_1$ ,  $W_2$ ,  $b_1$ ,  $b_2$ ) are all learnable parameters.

The output of the last sequencer block is entered into the linear classifier by one-layer normalisation and a global average pooling layer.

#### B. Overall Circuit Architecture

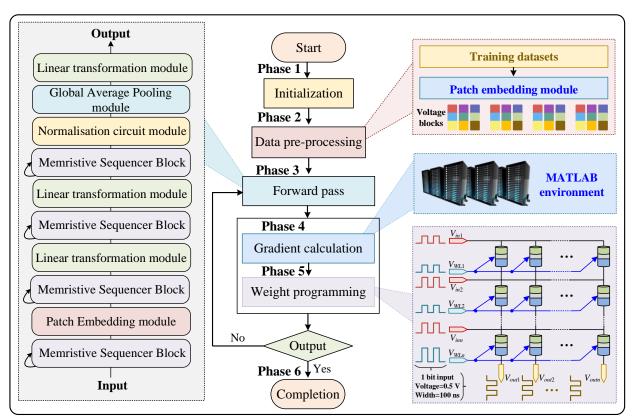

The structure of the proposed EMSN with sequencer blocks and necessary function modules is illustrated in **Fig. 5**.

Fig. 5. The structure of the proposed EMSN

The sequencer block circuit is the fundamental element of EMSN, which consists of three modules: BiLSTM2D circuit module, normalisation circuit module, and multi-layer perceptron module. The necessary function modules contain three function circuits: patch embedding module, global average pooling circuit module, and timing signal generation module. Specifically, the input images are converted into voltage signals via a digital-to-analogue converter. Voltage signals are rearranged into voltage blocks by the patch embedding module, and each signal is controlled by a timing signal. The corresponding row signal can be applied to other modules when the efficacy of the timing signal is evident. Once the last sequencer block is calculated, the linear classifier will output a set of voltage signals.

#### C. Circuit Design of Sequencer Block

## 1) BiLSTM2D circuit module

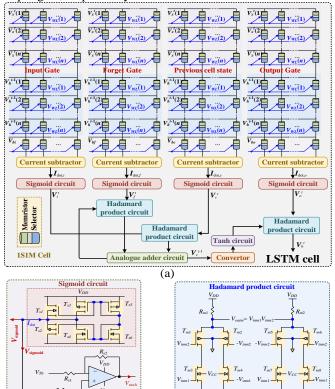

According to (1) - (5), the LSTM cell is the key to realising the BiLSTM2D circuit module, which mainly consists of four LSTM units to generate  $i_t$ ,  $f_t$ ,  $o_t$ , and  $c_t$ . The LSTM cell is designed using the memristive synapse arrays and some peripheral circuits, as shown in **Fig. 6(a)**. Notably, the sneak

path is a major obstacle to securing an increase in memristive synapse array size [24]. A potential approach is adopting selector, a type of nonlinear resistive device that conducts current only when the applied voltage exceeds a certain threshold (ON state); otherwise, selector allows little current to go through (OFF state) [25]. In this way, the memristive synapse arrays with the one-selector-one-Ag-Au/MoSe<sub>2</sub>doped Se/Au-Ag memristor (1S1M) configuration can conduct matrix-vector multiplication for each LSTM unit. The selector and memristor can be stacked on top of each other, giving a higher density potential than the one-transistor-one-memristor (1T1M) scheme. The input voltage  $V_x^t(n)$   $(n \in [1, N])$  belongs to time step t, and the hidden state voltage  $V_h^{t-1}(m)$   $(m \in [1, M])$ belongs to time step t-1. The  $V_{bi}$ ,  $V_{bf}$ ,  $V_{bc}$ , and  $V_{bo}$  are the bias voltages of the input gate, forget gate, previous cell state, and output gate, respectively.

**Fig. 6**. Circuit design of BiLSTM2D circuit module (a) LSTM cell; (b) activation circuits; (c) Hadamard product circuit

(c)

$R_{s4}$

In **Fig. 6(a)**, the weight of the LSTM unit is represented by the difference in conductance of two memristors in the memristive synapse array. The dot product currents  $I_{\text{dot}}$  from the current subtractors [26] are fetched into the corresponding activation circuit (i.e., sigmoid activation circuit and tanh activation circuit, labelled by the red/green rectangle in **Fig. 6(b)**). Specifically, the sigmoid activation circuit is composed of six transistors  $T_{s1}$ — $T_{s6}$ . The output voltage  $V_{\text{sigmoid}}$  and input current  $I_{\text{dot}}$  of the sigmoid activation circuit are located in the same node. Since the tanh function has the same shape as the sigmoid function, we use the output voltage of the sigmoid activation circuit as the input voltage of the tanh activation circuit that consists of an amplifier  $A_1$  with four resistors  $R_{s1}$ — $R_{s4}$ . Then, the output voltages  $V_i^t$ ,  $V_j^t$ ,  $V_j^t$ , of the input gate, forget

gate, and output gate can be produced from the activation circuits. Furthermore, the Hadamard product circuit is used to perform a pointwise operation, which consists of eight transistors  $T_{m1}$ — $T_{m8}$  and two resistors  $R_{m1}$  and  $R_{m2}$ , as shown in **Fig. 6(c)**.  $V_{inm1}$  and  $V_{inm2}$  are the inputs of the Hadamard product circuit, and  $V_{outm} = V_{inm1} \cdot V_{inm2}$  is the output of the Hadamard product circuit. Finally, the cell state voltage  $V_c^t$  and the cell output voltage  $V_h^t$  can be obtained after several steps of activation, multiplication, and summation, which are implemented by the activation circuit, Hadamard product circuit, and analogue adder circuit [26]. The calculation for  $V_i^t$ ,  $V_j^t$ ,  $V_o^t$ ,  $V_c^t$ ,  $V_h^t$  in **Fig. 6(a)** is provided below:

$$V_{i}^{t} = \sigma \begin{cases} \sum_{n=1}^{N} \left(G_{x,i}^{+} - G_{x,i}^{-}\right) V_{x}^{t}(n) \\ + \sum_{m=1}^{M} \left(G_{h,i}^{+} - G_{h,i}^{-}\right) V_{h}^{t-1}(m) + I_{bi} \end{cases}$$

$$V_{f}^{t} = \sigma \begin{cases} \sum_{n=1}^{N} \left(G_{x,f}^{+} - G_{x,f}^{-}\right) V_{x}^{t}(n) \\ + \sum_{m=1}^{M} \left(G_{h,f}^{+} - G_{h,f}^{-}\right) V_{h}^{t-1}(m) + I_{bf} \end{cases}$$

$$V_{c}^{t} = V_{f}^{t} \odot V_{c}^{t-1} + V_{i}^{t} \odot \tanh \begin{cases} \sum_{n=1}^{N} \left(G_{x,c}^{+} - G_{x,c}^{-}\right) V_{x}^{t}(n) \\ + \sum_{m=1}^{M} \left(G_{h,c}^{+} - G_{h,c}^{-}\right) V_{h}^{t-1}(m) + I_{bc} \end{cases}$$

$$V_{o}^{t} = \sigma \begin{cases} \sum_{n=1}^{N} \left(G_{x,o}^{+} - G_{x,o}^{-}\right) V_{x}^{t}(n) \\ + \sum_{m=1}^{M} \left(G_{h,o}^{+} - G_{h,o}^{-}\right) V_{h}^{t-1}(m) + I_{bo} \end{cases}$$

$$V_{b}^{t} = V_{o}^{t} \odot \tanh \left(V_{c}^{t}\right)$$

Based on this, the circuit design of BiLSTM2D can be obtained. It consists of four LSTM cells: backward LSTM cell in the vertical BiLSTM, forward LSTM cell in the vertical BiLSTM, backward LSTM cell in the horizontal BiLSTM, and forward LSTM cell in the horizontal BiLSTM.

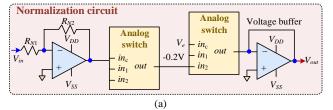

## 2) Normalisation circuit module

The normalisation circuit module is composed of an inverting amplifier with two resistors  $R_{N2}$  and  $R_{N1}$ , two analogue switch circuits, and a voltage buffer circuit. The inverting amplifier can linearly generate a stable voltage. The analogue switch circuit is used as the comparator, and the specific circuit implementation is shown in **Fig. 7(a)**. The analogue switch circuit is connected to the voltage buffer to reduce the loading effect from the upper circuit into the output of the normalisation circuit. We can normalise the upper circuit output to the range of  $-V_N$  to  $V_N$  using the normalisation circuit module.

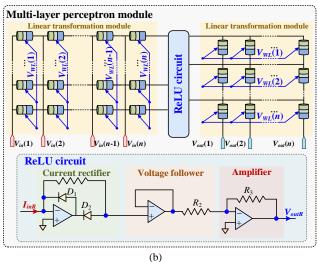

## 3) Multi-layer perceptron module

The multi-layer perceptron module consists of two memristive synapse arrays with a ReLU activation circuit in between, labelled by the yellow rectangle in **Fig. 7(b)**. The memristive synapse array with the 1S1M configuration is responsible for the linear transformation. The ReLU activation circuit is composed of a current rectifier, a voltage follower, and an amplifier (labelled by the blue rectangle in **Fig. 7(b)**). The current rectifier provides a compact design to generate rectified

$$V_{outR} = \begin{cases} \frac{R_1 R_3}{R_2} I_{inR}, I_{inR} \ge 0\\ 0, I_{inR} < 0 \end{cases}$$

(8)

**Fig. 7**. Circuit design of peripheral circuits (a) normalisation circuit module; (b) multi-layer perceptron module

#### D. Circuit Design of Necessary Function Modules

## 1) Patch embedding module

circuit is defined as:

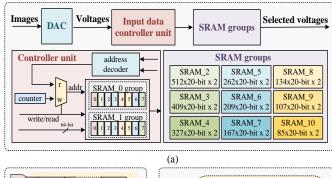

Fig. 8(a) illustrates the structure of the patch embedding module, which consists of an input data control unit and static random-access memory groups. The input images from the datasets are converted to voltage signals by the digital-to-analogue converter and sent to the input data control unit that selects the required number of voltage signals. Then, the selected voltage signals are stored in the static random-access memory groups. Depending on the size of the input images, the patch embedding module selects a parallel or serial processing type and rearranges the voltage signals into blocks, followed by subsequent processing.

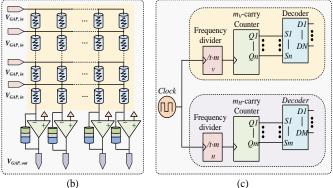

## 2) Global average pooling circuit module

Global average pooling (GAP) involves a convolution operation in which the convolution kernel values are equal. In addition, the GAP is unique, whereas the window and feature map sizes are equal. Accordingly, it is possible to determine the GAP circuit design. Instead of adopting a memristive synapse array, this study employs a basic summing circuit, as shown in **Fig. 8(b)**. The formula presented below indicates the mathematical meaning of the entire circuit:

$$V_{GAP,out} = \sum_{j=1}^{N} \left( V_{GAP,in} \times R_{j,i} \right) / \sum_{j=1}^{N} R_{j,i}, j = 1,...,N$$

(9)

where  $V_{GAP,in}$  and  $V_{GAP,out}$  are the input voltage and output voltage of the GAP circuit module, respectively; and  $R_{j,i}$  is the resistance in row j and column i.

## 3) Timing signal generation module

The proposed EMSN needs timing signals to schedule the input matrix and save the calculated results in sequence. The timing signal generation module is composed of a vertical timing generator and a horizontal timing generator, which exploits two sets of timing signals, the vertical timing signal VLs and the horizontal timing signal HLs, as shown in Fig. 8(c). The number of channels is  $m_V$  and  $m_H$ , respectively. For the VLs (HLs) signals, the clock frequency is reduced by  $m_V(m_H) \times t$  times by the frequency divider. Then, the output signals are counted by the  $m_V(m_H)$  counter. Finally, the decoder decodes the counting result into timing signals.

**Fig. 8**. Circuit design of necessary Function Modules (a) patch embedding module; (b) global average pooling circuit module; (c) timing signal generation module

The necessary circuit parameter settings of the proposed EMSN are provided in Table I.

TABLE I

THE NECESSARY CIRCUIT PARAMETERS SETTING

| Parameters | Values          | Parameters | Values                 | Parameters | Values       |

|------------|-----------------|------------|------------------------|------------|--------------|

| $T_{s1}$   | 20μ/0.18μ       | $T_{m8}$   | $2\mu/0.22\mu$         | $R_{s4}$   | 1kΩ          |

| $T_{s2}$   | $20\mu/0.18\mu$ | $T_{N1}$   | $3\mu/0.18\mu$         | $R_{N1}$   | $1k\Omega$   |

| $T_{s3}$   | $19\mu/0.18\mu$ | $T_{N2}$   | $30\mu/0.18\mu$        | $R_{N2}$   | $1k\Omega$   |

| $T_{s4}$   | $18\mu/0.18\mu$ | $T_{N3}$   | $36\mu/0.18\mu$        | $R_{N3}$   | $10k\Omega$  |

| $T_{s5}$   | $20\mu/0.18\mu$ | $T_{N4}$   | $36\mu/0.18\mu$        | $R_{r1}$   | $10k\Omega$  |

| $T_{s6}$   | $20\mu/0.18\mu$ | $T_{N5}$   | $6\mu/0.18\mu$         | $R_{r2}$   | $10k\Omega$  |

| $T_{m1}$   | $1.6\mu/0.3\mu$ | $T_{N6}$   | $6\mu/0.18\mu$         | $R_{r3}$   | $1k\Omega$   |

| $T_{m2}$   | $1.6\mu/0.3\mu$ | $T_{N7}$   | $45\mu/0.3\mu$         | $V_{Tb}$   | 0.5V         |

| $T_{m3}$   | $2\mu/0.22\mu$  | $T_{N8}$   | $18\mu/0.3\mu$         | $V_{DD}$   | 1.8V         |

| $T_{m4}$   | $2\mu/0.22\mu$  | $T_{N9}$   | 18μ/0.3μ               | $V_S$      | -1.8V        |

| $T_{m5}$   | $1.6\mu/0.3\mu$ | $R_{s1}$   | 1kΩ                    | $C_N$      | 1 <i>p</i> F |

| $T_{m6}$   | $1.6\mu/0.3\mu$ | $R_{s2}$   | $1.7 \mathrm{k}\Omega$ | $R_{i,i}$  | 1kΩ          |

| $T_{m7}$   | $2\mu/0.22\mu$  | $R_{s3}$   | 1kΩ                    | -          | -            |

Fig. 9. The flow chart of hardware friendly training phase

#### IV. APPLICATION IN HUMAN EMOTION CLASSIFICATION

Facial expression plays an important role in daily life, enabling the mental health state of an individual to be conveyed and inferred. In this section, the proposed EMSN is applied to human emotion classification to provide an efficient and fast solution for health monitoring and disease management. To verify the feasibility and effectiveness of the proposed system, a series of experiments are carried out by comparing the proposed system with competitors.

## A. Database and Evaluation Metrics

The proposed system is evaluated on two human emotion classification datasets: the FER2013 dataset and the extended Cohn-Kanade dataset (CK+) [27]. The FER2013 dataset is a large-scale and unconstrained database, which comprises 35,887 greyscale face images of size 48 48. Following previous works, 3,589 samples are distributed in a validation dataset, 3,589 in a testing dataset, and the remaining 28,709 in a training dataset. Each face has one of seven emotion labels: "angry", "disgust", "fear", "happy", "sad", "surprised" and "neutral". The CK+ dataset consists of 593 video sequences from 123 subjects. Each video sequence in CK+ dataset has segmented from neutral frame to peak frame of facial expressions about 10-60 frames. The last frame of each sequence is labelled with one of seven expressions ("angry", "disgust", "fear", "happy", "sad", "surprised" and "neutral"). To collect sufficient images for training, we extract the neutral frames and the final three frames with peak formation from the labelled sequence to generate 1,236 expression images. Following previous works, 309 samples in a testing dataset, and the remaining 927 in a training dataset. Then, the common performance metric of average accuracy is used to evaluate the overall performance.

#### B. Hardware Friendly Training Method

The neural network is trained, and the entire process can be divided into two parts: the feedforward computation and back propagation. The feedforward computation is carried out in the proposed EMSN; the back propagation (mainly referring to the weight updating) is performed in MATLAB 2018b. The specific training method with six phases is illustrated in **Fig. 9**.

**Phase 1.** Initialisation: At the beginning, the conductances of all Ag-Au/MoSe<sub>2</sub>-doped Se/Au-Ag memristors in the 1S1M array are initialised to an appropriate value by setting the voltage across the memristors.

**Phase 2.** Data pre-processing: The input images from the training datasets are converted to voltage blocks within the range of [-3, 3] via the patch embedding module.

**Phase 3.** Forward pass: The voltage blocks are injected into the proposed EMSN, after which the corresponding output voltage can be achieved.

**Phase 4.** Error backpropagation: The error backpropagation through the stochastic gradient descent approach by a factor of  $10^{-4}$  is adopted to compute the intended conductance update values. This is performed in the MATLAB environment (R2018b).

**Phase 5.** Weight update: The conductance is updated on a row-by-row or column-by-column basis, as proposed in [28]. Evidence exists of the effectiveness of the two-pulse scheme as

a means of realising linear and symmetric memristor conductance updates.

**Phase 6.** Completion: after the entire EMSN settles, the training process is completed; otherwise, return to **Phase 3**.

This hardware friendly training method combines the advantages of the energy efficiency of the 1S1M synapse array in performing the analogue MAC operation and the digital logic for realising the rest of the training process.

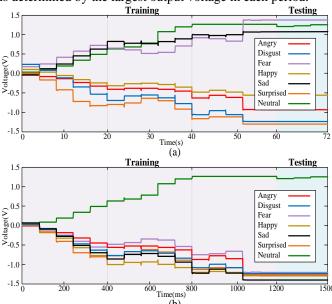

## C. Human Emotion Classification Results and Analysis

The proposed EMSN is used to demonstrate human emotion classification. Fig. 10 illustrates the circuit progresses of the training and testing processes when identifying the expressions of emotion of the FER2013 dataset and the CK+ dataset. The corresponding output voltage can be achieved with seven states (assigned to corresponding emotion expressions), as shown in Fig. 10(a) and Fig. 10(b). Once the training process is completed, the classifier will output a set of voltage signals representing a probability distribution. The classification result is determined by the largest output voltage in each period.

**Fig. 10**. The corresponding results obtained by the proposed EMSN (a) FER2013 dataset; (b) CK+ dataset

The proposed EMSN is compared with the state-of-the-art methods on the FER2013 dataset and the CK+ dataset, as shown in Table II.

TABLE II

COMPARISON OF DIFFERENT STATE-OF-THE-ART METHODS

IN HUMAN EMOTION CLASSIFICATION

| References | FER2013 |         | CK+    |         |

|------------|---------|---------|--------|---------|

| References | Acc.    | Time    | Acc.   | Time    |

| [29]       | 70.19   | 457.52  | 94.47  | 160.372 |

| [30]       | 73.96   | 502.77  | 97.10  | 221.22  |

| [31]       | 72.47   | 389.232 | 97.83  | 178.29  |

| [32]       | 72.36   | 455.163 | 97.35  | 202.53  |

| [33]       | 74.982  | 524.76  | 98.893 | 193.86  |

| [34]       | 84.301  | 523.82  | 99.301 | 164.523 |

| [35]       | 74.09   | 495.38  | -      | 192.33  |

| [36]       | 74.21   | 535.43  | 97.72  | 220.84  |

| This work  | 74.663  | 28.421  | 98.912 | 13.921  |

Note: the subscript 1, 2, 3 represent the corresponding ranking results.

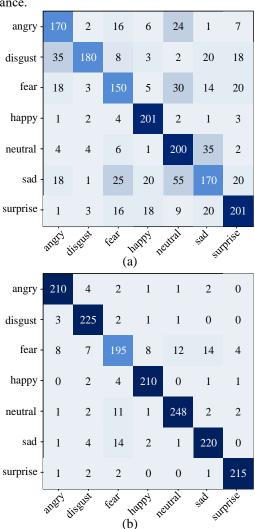

From Table II, the proposed network ranks in the top three on the FER2013 dataset and slightly outperforms other competitors [29-32, 35, 36]. On the CK+ dataset, it outperforms state-of-the-art methods in the human emotion classification task [29-33, 35, 36]. Meanwhile, [33, 34] are slightly superior to the proposed method in terms of accuracy, while inferior to time consumption. The results demonstrate that the trade-off between the accuracy and time consumption can be well balanced in the proposed memristive sequencer network. Fig. 11 shows the confusion matrixes of the proposed EMSN on the FER2013 testing dataset and the CK+ testing dataset. As shown in Fig. 11, the "sad" emotion expression is confused with the "neutral" emotion for the FER2013 dataset. The most difficult expression of emotion is "fear", which has the lowest recognition rates for both the CK+ and FER2013 datasets. Although the training data are unbalanced, the proposed network overcomes this problem and improves the overall performance.

**Fig. 11.** Confusion matrix (a) FER2013 dataset; (b) CK+dataset

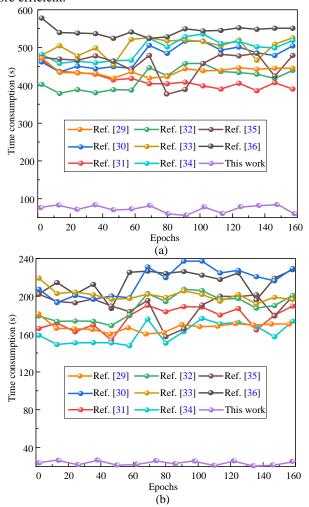

#### D. Computational Efficiency

Due to the speed advantage of the hardware implementation of the sequencer network, the proposed system has benefits in computational efficiency in terms of time, power. The time consumption of the proposed EMSN is analysed by comparing

it with a competitor on the FER2013 dataset and the CK+ dataset, as shown in **Fig. 12**. The proposed network is faster (approximately 10–20 times) than other software-based neural networks. The explanation for this difference may be that parallel-computing via 1S1M memristive synapse arrays is more efficient.

**Fig. 12**. The time consumption of the proposed EMSN (a) FER2013 dataset; (b) CK+ dataset

## TABLE III THE ENERGY CONSUMPTION OF EMSN

| Module                                | Power consumption/pJ |  |

|---------------------------------------|----------------------|--|

| BiLSTM2D circuit module               | 226.73               |  |

| Normalization circuit module          | 27.22                |  |

| Multi-layer perceptron module         | 78.22                |  |

| Patch embedding module                | 327.45               |  |

| Global average pooling circuit module | 10.66                |  |

| Timing signal generation module       | 11.27                |  |

| Total                                 | 2057.98              |  |

Table III presents the energy consumption for each circuit module and the entire circuit. The energy consumption for 1-bit computing is 2,057.98 pJ, and the power consumption for 1-bit computing is 20.58 mW with 0.5 V and 100 ns read voltage. The circuit is executed using 180-nm CMOS technology, and the total area of the proposed system is approximately  $48.63~\mu m^2$ . In addition, the benefits of the proposed network include time, power, and area advantages. These are indicative of the cost-saving and energy-efficient character of the proposed system.

#### E. Robustness Analysis

For practical applications, it is necessary to analyse the robustness of the proposed EMSN for human emotion.

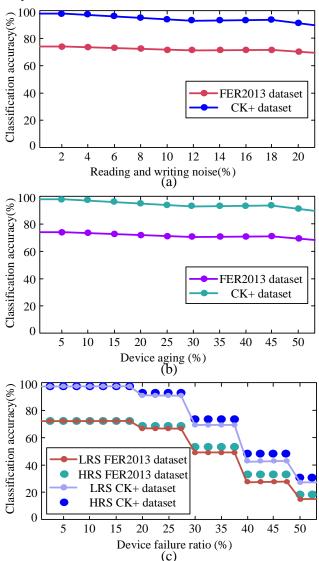

## 1) Anti-noise analysis

Considering that the standard deviation of reading and writing noise may be inevitable in signal transmission and processing, we added reading and writing noise to the proposed network. The human emotion classification accuracy is demonstrated in **Fig. 13(a)**. When the standard deviation of reading and writing noise is over 20%, the classification accuracy can be kept over 70% and 90% on the FER2013 dataset and CK+ dataset, respectively. The experiment results demonstrate that the proposed network has good anti-noise ability.

**Fig. 13**. Robustness Analysis of the proposed EMSN (a) antinoise analysis; (b) device aging analysis; (c) device failure analysis

## 2) Device aging and failure analysis

Device aging or failure may lead to the conductance drifting or deviating from the correct state [37]. As shown in **Fig. 13(b)**, when the percentage of aging reaches about 50%, the classification accuracy can be kept over 70% and 90% on the

FER2013 dataset and CK+ dataset, respectively. The experiment result illustrates that device aging does not affect the classification accuracy of the proposed system. The effect of device failure on the classification accuracy of the proposed network is illustrated in **Fig. 13(c)**. When the memristor is in LRS/HRS and the failure ratio reaches about 25%, the classification accuracy can be maintained at an acceptable level (over 67% and 88% on the FER2013 dataset and CK+ dataset, respectively). Once the memristor failure ratio exceeds 30%, the accuracy decreases sharply to about 20%. Thus, the experiment shows that the proposed EMSN can tolerate up to 25% failed devices within the architecture.

The reason maybe that the adjustment of the network weight is rather an overall value of 1S1M synapse array than an exact value of each memristor. Therefore, the performance of the proposed network will not be strongly affected by reading and writing noise, device aging, and device failure.

#### V. CONCLUSION

In this work, we investigate an energy-efficiency memristive sequencer network. Firstly, a kind of eco-friendly memristor is fabricated using 2D materials, and the corresponding testing performance is conducted to make sure its efficiency and stability. Then, the memristor-based sequencer block consisting of BiLSTM2D circuit module, normalization circuit module, and multi-layer perceptron module is proposed. Based on this, the circuit design of the proposed EMSN can be achieved after combining some other necessary function circuit modules (i.e., patch embedding module, global average pooling circuit module, and timing signal generation module). Furthermore, the proposed EMSN is applied for human emotion classification. The experimental results demonstrate the good performance of the proposed EMSN, especially in classification accuracy, computational efficiency, and robustness. This work provides a new way to achieve the deep integration of multimedia processing and neuromorphic computing, which is expected to promote the development of consumer electronics applications.

Notably, the energy-efficient memristive sequencer network is still in an infancy stage with abundant opportunities and challenges. To further develop and apply this work into the real life, several aspects can be considered in future research: At the algorithmic level, the main training process in this work is completed via software platform. The desired memristive conductance obtained by MATLAB environment (R2018b) is directly mapped to the proposed network without read or write to memristive synapse array. Thus, the general learning circuit module will be designed to perform back-propagation operation. At system level, the human perception function is not considered in this work, the perception data directly comes from existing human emotion classification datasets. This work will be extended to integrate the brain-inspired approach, wearable technology, and nanotechnology for consumer health monitoring. Specifically, the brain-inspired system for sensing and processing multimodal information in real-time manner will be developed. The entire system is expected to be integrated into a wearable device for consumer health monitoring.

#### REFERENCES

- [1] P. P. Ray, N. Thapa and D. Dash, "Implementation and performance analysis of interoperable and heterogeneous IoT-edge gateway for pervasive wellness care," *IEEE Trans. Consum. Electron.*, vol. 65, no. 4, pp. 464-473, 2019, doi: 10.1109/TCE.2019.2939494.

- [2] R. Chatterjee, S. Mazumdar, R. S. Sherratt, R. Halder, T. Maitra and D. Giri, "Real-time speech emotion analysis for smart home assistants," *IEEE Trans. Consum. Electron.*, vol. 67, no. 1, pp. 68-76, 2021, doi: 10.1109/TCE.2021.3056421.

- [3] S. Saeed, M. K. Mahmood, and Y. D. Khan, "An exposition of facial expression recognition techniques," *Neural Comput. Appl.*, vol. 29, no. 9, pp. 425-443, 2018, doi:10.1007/s00521-016-2522-2.

- [4] A. Barman, and P. Dutta, "Facial expression recognition using distance and texture signature relevant features," *Appl. Soft Comput. J.*, vol. 77, pp. 88-105, 2019, doi:10.1016/j.asoc.2019.01.011.

- [5] H. Sadeghi, and A. A. Raie, "HistNet: Histogram-based convolutional neural network with Chi-squared deep metric learning for facial expression recognition," *Inf. Sci.*, vol. 608, pp. 472-488, 2022, doi:10.1016/j.ins.2022.06.092.

- [6] W. Yu, and H. Xu, "Co-attentive multi-task convolutional neural network for facial expression recognition," *Pattern Recognit.*, vol. 123, pp. 108401, 2022, doi:10.1016/j.patcog.2021.108401.

- [7] S. Liu, H. Wang, and M. Pei, "Facial-expression-aware emotional color transfer based on convolutional neural network," ACM Trans. Multimed. Comput. Commun. Appl., vol. 18, no. 1, pp. 1-19, 2022, doi:10.1145/3464382.

- [8] H. Zhang, B. Huang, and G. Tian, "Facial expression recognition based on deep convolution long short-term memory networks of double-channel weighted mixture," *Pattern Recognit. Lett.*, vol. 131, pp. 128-134, 2020, doi:10.1016/j.patrec.2019.12.013.

- [9] L. Tang, H. Wang, W. Zhang, Z. Mei, and L. Li, "Driver lane change intention recognition of intelligent vehicle based on long short-term memory network," *IEEE Access*, vol. 8, pp. 136898-136905, 2020, doi:10.1109/ACCESS.2020.3011550.

- [10] G. Du, Z. Wang, B. Gao, S. Mumtaz, K. M. Abualnaja, and C. Du, "A convolution bidirectional long short-term memory neural network for driver emotion recognition," *IEEE Trans. Intell. Transp. Syst.*, vol. 22, no. 7, pp. 4570-4578, 2021, doi:10.1109/TITS.2020.3007357.

- [11] Z. Dong, X. Ji, C. S. Lai, D. Qi, G. Zhou, and L. L. Lai, "Memristor-based hierarchical attention network for multimodal affective computing in mental health monitoring," *IEEE Consum. Electron. Mag.*, pp. 3159350, 2022, doi:10.1109/MCE.2022.3159350.

- [12] X. Ji, Z. Dong, C. S. Lai, and D. Qi, "A brain-inspired in-memory computing system for neuronal communication via memristive circuits," *IEEE Commun. Mag.*, vol. 60, no. 1, pp. 100-106, 2022, doi: 10.1109/MCOM.001.21664.

- [13] Z. Dong, X. Ji, C. S. Lai, and D. Qi, "Design and implementation of a flexible neuromorphic computing system for affective communication via memristive circuits," *IEEE Commun. Mag.*, vol. 61, no. 1, pp. 74-80, 2022, doi: 10.1109/MCOM.001.2200272.

- [14] X. Ji, Z. Dong, C. S. Lai, G. Zhou, and D. Qi, "A physics-oriented memristor model with the coexistence of NDR effect and RS memory behavior for bio-inspired computing," *Mater. Today Adv.*, vol. 16, pp. 100293, 2022, doi:10.1016/j.mtadv.2022.100293.

- [15] L. O. Chua, and L. Yang, "Cellular neural networks: Theory," *IEEE Trans. Circuits Syst.*, vol. 35, no. 10, pp. 1257-1272, 1988, doi:10.1109/31.7600.

- [16] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, no. 7191, pp. 80-83, 2008, doi:10.1038/nature06932.

- [17] F. Kiani, J. Yin, Z. Wang, J. Joshua Yang, and Q. Xia, "A fully hardware-based memristive multilayer neural network," *Sci. Adv.*, vol. 7, no. 48, pp. eabj4801, 2021, doi:10.1126/sciadv.abj4801.

- [18] C. Yang, X. Wang, and Z. Zeng, "Full-circuit implementation of transformer network based on memristor," *IEEE Trans. Circuits Syst.*, vol. 69, no. 4, pp. 1395-1407, 2022, doi:10.1109/TCSI.2021.3136355.

- [19] Z. Dong, X. Ji, G. Zhou, M. Gao, and D. Qi, "Multimodal neuromorphic sensory-processing system with memristor circuits for smart home applications," *IEEE Trans. Ind. Appl.*, pp. 3188749, 2022, doi:10.1109/TIA.2022.3188749.

- [20] Y. Tatsunami, and M. Taki, "Sequencer: Deep LSTM for image classification," arXiv preprint, pp. arXiv:2205.01972, 2022.

- [21] K. Liao, P. Lei, M. Tu, S. Luo, T. Jiang, W. Jie, and J. Hao, "Memristor based on inorganic and organic two-dimensional materials: mechanisms, performance, and synaptic applications," ACS Appl. Mater. Interfaces.,

- vol. 13, no. 28, pp. 32606-32623, 2021, doi:10.1021/acsami.1c07665.

- [22] K. Han, A. Xiao, E. Wu, J. Guo, C. Xu, and Y. Wang, "Transformer in transformer," Adv. Neural Inf. Process. Syst., vol. 19, pp. 15908-15919, 2021.

- [23] C. Tang, Y. Zhao, G. Wang, C. Luo, W. Xie, and W. Zeng, "Sparse MLP for image recognition: Is self-attention really necessary?," *Proc. AAAI Conf. Artif. Intell.*, vol. 36, no. 2, pp. 2344-2351, 2022, doi:10.1609/aaai.v36i2.20133.

- [24] H. Li, S. Wang, X. Zhang, W. Wang, R. Yang, Z. Sun, W. Feng, P. Lin, Z. Wang, L. Sun, and Y. Yao, "Memristive crossbar arrays for storage and computing applications," *Adv. Intell. Syst.*, vol. 3, no. 9, pp. 2100017, 2021, doi:10.1002/aisy.202100017.

- [25] C. Tsioustas, P. Bousoulas, J. Hadfield, T. P. Chatzinikolaou, I.-A. Fyrigos, V. Ntinas, M.-A. Tsompanas, G. C. Sirakoulis, and D. Tsoukalas, "Simulation of low power self-selective memristive neural networks for in situ digital and analogue artificial neural network applications," *IEEE Trans. Nanotechnol.*, vol. 21, pp. 505-513, 2022, doi:10.1109/TNANO.2022.3205698.

- [26] K. Smagulova, O. Krestinskaya, and A. James, "Who is the winner? Memristive-CMOS hybrid modules: CNN-LSTM versus HTM," *IEEE Trans. Biomed. Circuits Syst.*, vol. 14, no. 2, pp. 164-172, 2020, doi:10.1109/TBCAS.2019.2956435.

- [27] Y. Wu, and J. Li, "Multi-modal emotion identification fusing facial expression and EEG," *Multimed. Tools Appl.*, pp. 1-19, 2022, doi:10.1007/s11042-022-13711-4.

- [28] N. Vasileiadis, V. Ntinas, I. A. Fyrigos, R. E. Karamani, V. Ioannou-Sougleridis, P. Normand, I. Karafyllidis, G. C. Sirakoulis, and P. Dimitrakis, "A new 1P1R image sensor with in-memory computing properties based on silicon nitride devices," IEEE Intl. Sym. Circ. Syst. (ISCAS), Daegu, Korea, 22-28 May 2021: IEEE, pp. 1-5.

- [29] W. Xie, X. Jia, L. Shen, and M. Yang, "Sparse deep feature learning for facial expression recognition," *Pattern Recognit.*, vol. 96, pp. 106966, 2019, doi:10.1016/j.patcog.2019.106966.

- [30] J. Li, K. Jin, D. Zhou, N. Kubota, and Z. Ju, "Attention mechanism-based CNN for facial expression recognition," *Neurocomputing*, vol. 411, pp. 340-350, 2020, doi:10.1016/j.neucom.2020.06.014.

- [31] W. Xie, W. Chen, L. Shen, J. Duan, and M. Yang, "Surrogate network-based sparseness hyper-parameter optimization for deep expression recognition," *Pattern Recognit.*, vol. 111, pp. 107701, 2021, doi:10.1016/j.patcog.2020.107701.

- [32] W. Xie, L. Shen, and J. Duan, "Adaptive weighting of handcrafted feature losses for facial expression recognition," *IEEE Trans. Cybern.*, vol. 51, no. 5, pp. 2787-2800, 2021, doi:10.1109/TCYB.2019.2925095.

- [33] S. Li, W. Li, S. Wen, K. Shi, Y. Yang, P. Zhou, and T. Huang, "Auto-FERNet: A facial expression recognition network with architecture search," *IEEE Trans. Netw. Sci. Eng.*, vol. 8, no. 3, pp. 2213-2222, 2021, doi:10.1109/TNSE.2021.3083739.

- [34] M. Li, H. Xu, X. Huang, Z. Song, X. Liu, and X. Li, "Facial expression recognition with identity and emotion joint learning," *IEEE Trans. Affect. Comput.*, vol. 12, no. 2, pp. 544-550, 2021, doi:10.1109/TAFFC.2018.2880201.

- [35] H. D. Nguyen, S. H. Kim, G. S. Lee, H. J. Yang, I. S. Na, and S. H. Kim, "Facial Expression Recognition Using a Temporal Ensemble of Multi-Level Convolutional Neural Networks," *IEEE Trans. Affect. Comput.*, vol. 13, no. 1, pp. 226-237, 2022, doi:10.1109/TAFFC.2019.2946540.

- [36] S. Li, and W. Deng, "A deeper look at facial expression dataset bias," IEEE Trans. Affect. Comput., vol. 13, no. 2, pp. 881-893, 2022, doi:10.1109/TAFFC.2020.2973158.

- [37] A. James, Y. Toleubay, O. Krestinskaya and C. Reghuvaran, "Inference dropouts in binary weighted analog memristive crossbar," IEEE Trans. Nanotechnol., vol. 21, pp. 271-277, 2022, doi: 10.1109/TNANO.2022.3182244.

Xiaoyue Ji (Student Member, IEEE) received the B.E. degree in electronics and information engineering in 2016 degree from the School of Electrical Engineering, Harbin Engineering University, China. She is currently working toward the Ph.D. degree in control theory and control engineering from the School of Electrical Engineering, Zhejiang University, China.

Her research interests cover memristor and memristive system, artificial neural network, the design and analysis of nonlinear systems based on memristor and computer simulation.

Zhekang Dong (Senior Member, IEEE) received the B.E. and M.E. degrees in electronics and information engineering in 2012 and 2015, respectively, from Southwest University, Chongqing, China. He received the Ph.D. degree from the School of Electrical Engineering, Zhejiang University, China, in 2019. Currently, he is an associate professor in Hangzhou Dianzi

University, Hangzhou, China. He is also a Research Assistant (Joint-Supervision) at The Hong Kong Polytechnic University. His research interests cover memristor and memristive system, artificial neural network, the design and analysis of nonlinear systems based on memristor and computer simulation.

Yifeng Han received the B.E. degrees in automation in 2017 from Zhejiang University. He received the M.E. degrees in control system from Imperial College London in 2018. Currently, he is studying for the Ph.D. degree in Electrical engineering from Zhejiang University. His current research interests cover image processing and data analysis.

Chun Sing Lai (Senior Member, IEEE) received the BEng in electronic and electrical engineering from Brunel University London, UK, and DPhil in engineering science from the University of Oxford, UK in 2013 and 2019, respectively. Dr Lai is currently a Lecturer at the Department of Electronic and Electrical Engineering, Brunel University London,

UK. His current interests are in data analytics, power system optimization, energy system modelling, and energy economics for low carbon energy networks and energy storage systems.

Guangdong Zhou has received his PhD in Faculty of Materials and Energy from Southwest University (P. R. China) in June 2018. He is conducting his postdoctoral research in the Southwest University during 2018.07–2020.07. His research focus on the physical mechanism of memristor, memristor-based functions including the memory logics, displays and

synapses. His memristor related researches are supported by the Postdoctoral Program for Innovative Talent Support of Chongqing (600 thousand RMB). During past 5years, more than 50 peer reviewed papers were published. Dr. Zhou sincerely thirsts for the communication and cooperation from broad researcher

Donglian Qi (Senior Member, IEEE) received the Ph.D. degree in control theory and control engineering from the School of Electrical Engineering, Zhejiang University, China, in 2002. She is currently a Full Professor and a Ph.D. Advisor with Zhejiang University. Her recent research interest covers intelligent information processing, chaos system, and nonlinear

theory and application.